ZFx86<sup>TM</sup>

System-on-a-Chip

**Data Book**

Version 1.0 Rev D

June 5, 2006

THIS DOCUMENT AND THE INFORMATION CONTAINED THEREIN IS PROVIDED "AS-IS" AND WITHOUT A WARRANTY OF ANY KIND. YOU, THE USER, ACCEPT FULL RESPONSIBILITY FOR PROPER USE OF THE MATERIAL. ZF MICRO SOLUTIONS, INC. MAKES NO REPRESENTATIONS OR WARRANTIES THAT THIS DATA BOOK OR THE INFORMATION CONTAINED THERE-IN IS ERROR FREE OR THAT THE USE THEREOF WILL NOT INFRINGE ANY PATENTS, COPYRIGHT OR TRADEMARKS OF THIRD PARTIES. ZF MICRO SOLUTIONS, INC. EXPLICITLY ASSUMES NO LIABILITY FOR ANY DAMAGES WHATSOEVER RELATING TO ITS USE.

#### LIFE SUPPORT and HIGH RISK APPLICATION POLICY

Customers of ZF Micro Solutions products will not knowingly integrate, promote, sell, or otherwise transfer any ZF Product to any customer or end user for use in any high risk applications, LIFE SUPPORT DEVICES or Life support SYSTEMS.

ZF MICRO SOLUTIONS' PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COM-PONENTS IN HIGH RISK APPLICATIONS or LIFE SUPPORT DEVICES or LIFE SUPPORT SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GEN-ERAL COUNSEL OF ZF MICRO SOLUTIONS, INC. and ZF Micro Solutions does not indemnify for any such uses.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

- 3. A high risk application is any use in any applications where it is reasonably foreseeable that failure of the product as used in such application(s) would lead to death, bodily injury, or catastrophic property damage. Examples of such applications specifically include, without limitation, certain uses in nuclear facilities, air traffic control systems, and aeronautical aircraft control applications.

- © 2001 ZF Micro Devices, Inc. All rights reserved.

- © 2006 ZF Micro Solutions, Inc. All rights reserved.

ZFx86, FailSafe FailSafe Boot ROM, Z-tag ZF-Logic, InternetSafe, OEMmodule SCC, ZF SystemCard, ZF FlashDisk-SC, netDisplay, ZF 104Card, ZF SlotCard, and ZF Micro Solutions logo are trademarks of ZF Micro Solutions, Inc. Other brands and product names are trademarks of their respective owners.

All trademarks and copyrights of ZF MicroSystems, ZF Embedded, ZF Linux Devices and ZF Micro Devices are the property of ZF Micro Solutions.

### **ZFx86 Specification Changes**

This application note describes the differences in specifications between the ZFx86BGA388 devices produced for ZF Micro Solutions by National Semiconductor and the new devices available as of June 1, 2006 produced for ZF Micro Solutions by IBM Microelectronics.

#### **DEVICE MARKING**

NSC produced devices had the following foundry code: 3100-0200-01 B1 or 3100-0200-01 A5

IBM produced devices have the following foundry code: 3100-0200-03 C0

#### **CPU PERFORMANCE**

Initial units of the IBM produced devices will be available at 100 MHz CPU clock speeds.

(NSC produced versions were: Industrial temp 100MHz; Commercial temp 128MHz)

#### **VOLTAGE**

# NOTE: IF YOU WILL BE TESTING THE NEW ZFx86 ON AN EXISTING DESIGN THE CORE VOLTAGE MUST BE CHANGED TO THE SETTING BELOW!

The Vdd-Core voltage specification is expected to be:

Minimum 2.09V

Nominal 2.20V

Maximum 2.31V

(NSC produced versions were also dual voltage devices: 5V tolerant, 3.3V I/O, 2.5V core voltage at 100MHz and 2.7V core voltage at 128MHz)

### **MECHANICAL / ENVIRONMENTAL**

Commercial Temperature - Up to 100MHz (0C to +70C ambient temperature)

Industrial Temperature - Up to 100MHz (-40C to +85C case temperature)

Package: 388-pin Plastic Ball Grid Array, 35mm x 35mm, fully RoHS compliant

(NSC produced versions were non RoHS compliant)

NOTE: After full characterization of the devices from the IBM foundry has been completed ZF will issue an update regarding final temperature ratings.

#### **SOFTWARE**

An updated version of the ZTAG .bin file for loading the Phoenix BIOS is required however there is no change to the BIOS, just this particular loader module.

Please contact **support@zfmicro.com** with "NEW Z-TAG" in the subject line and you will be sent the new file.

Note: When you flash the BIOS using the dongle there are two software components inside of the dongle; the loader program and the BIOS image. You will now use a new version of the loader program but the same BIOS image.)

### **Revision History**

This section contains the revision history of this manual, starting with ZFx86 Data Book 1.0 Revision D. The change from revision C to revision D occurred when ZF Micro Solutions resumed production of the ZFx86 using a new foundry in 2006. Designers who used ZFx86 chips in pre-2006 products will want to review the specification changes listed herein.

### Volume I Revision D June 5th, 2006

Most references to ZF Micro Devices are changed to ZF Micro Systems (except in copyright of source code listings).

The specification for Vdd-Core has been changed to new voltages in <u>Table 7.2</u>, 'Recommended <u>Operating Conditions</u>,' on page 482

A note listing important changes between the NSC (previous) and IBM (current) produced chips appears on <u>"ZFx86 Specification Changes" on page 4</u>

| ZFx86 Specification Changes          | 4   |

|--------------------------------------|-----|

| Revision History                     |     |

| Volume I Revision D June 5th, 2006   | 6   |

| Table of Contents                    | 7   |

| List of Figures                      | 13  |

| List of Tables                       | 17  |

| 1. Overview                          |     |

| 2. 32-bit x86 Processor              | 31  |

| 2.1. Overview                        | 31  |

| 2.1.1. Internal Clock Logic          |     |

| 2.1.2. On-Chip Write-Back Cache      |     |

| 2.1.3. System Management Mode        |     |

| 2.1.4. Power Management              |     |

| 2.1.5. Signal Summary                |     |

| 2.2. Programming Interface           |     |

| 2.2.1. Processor Initialization      | 34  |

| 2.2.2. Instruction Set Overview      | 35  |

| 2.2.3. Register Set                  | 36  |

| 2.2.4. Address Spaces                | 60  |

| 2.2.5. Interrupts and Exceptions     | 66  |

| 2.2.6. System Management Mode        | 71  |

| 2.2.7. Shutdown and Halt             | 80  |

| 2.2.8. Protection                    | 80  |

| 2.2.9. Virtual 8086 Mode             | 82  |

| 2.2.10. FPU Operations               | 83  |

| 2.3. Instruction Set                 | 86  |

| 2.3.1. General Instruction Fields    | 87  |

| 2.3.2. Instruction Set Tables        | 93  |

| 3. North Bridge                      | 113 |

| 3.1. North Bridge Features           | 113 |

| 3.2. Interface Signals               |     |

| 3.3. Functional Description          |     |

| 3.3.1. Processor Interface           |     |

| 3.3.2. DRAM Controller               |     |

| 3.3.3. Configuration and Testability |     |

| 3.3.4. PCI bus interface and arbiter |     |

| 3.3.5. PCI Write Buffer and Bursts   |     |

| 3.3.6. Write buffer architecture     |     |

| 3.3.7. System Management Mode        |     |

| 3.3.8. Power Management              |     |

| 3.4. Register Set                    | 136 |

|       | 3.4.1. Register Address Map                                       | 137 |

|-------|-------------------------------------------------------------------|-----|

|       | 3.4.2. DRAM registers                                             | 149 |

|       | 3.4.3. Power Management registers                                 | 160 |

|       | 3.4.4. Test Signals                                               | 162 |

|       | 3.4.5. PCI configuration registers                                | 162 |

| 4. So | outh Bridge                                                       | 165 |

| 4     | .1. South Bridge Module                                           | 165 |

|       | 4.1.1. South Bridge Features                                      | 165 |

| 4     | .2. Architecture                                                  |     |

|       | 4.2.1. Front-side PCI / Back-Side PCI Bus                         | 167 |

|       | 4.2.2. IDE Controller                                             |     |

|       | 4.2.3. Universal Serial Bus                                       |     |

|       | 4.2.4. Integrated SuperI/O                                        |     |

|       | 4.2.5. ISA Bus Interface                                          |     |

|       | 4.2.6. Power Management                                           |     |

|       | 4.2.7. GPIO Interface                                             | 171 |

|       | 4.2.8. ZF-Logic                                                   |     |

| 4     | .3. Signal Descriptions                                           |     |

|       | 4.3.1. System Interface Signals                                   |     |

|       | 4.3.2. Back-Side PCI Interface Signals                            |     |

|       | 4.3.3. Integrated SuperI/O Interface Signals                      |     |

| 4     | .4. Register Descriptions                                         |     |

|       | 4.4.1. PCI Configuration Space and Access Methods                 |     |

|       | 4.4.2. Register Summaries                                         |     |

|       | 4.4.3. Chipset Register Space                                     |     |

|       | 4.4.4. USB Controller Registers - PCIUSB                          |     |

| 4     | 4.4.5. ISA Legacy Register Space                                  |     |

| 4     | .5. SuperI/O - A PC98 Compliant Cell                              |     |

|       | 4.5.2. Features                                                   |     |

|       | 4.5.3. SIGNAL/PIN Descriptions                                    |     |

|       | 4.5.4. Device Architecture and Configuration                      |     |

|       | 4.5.5. Standard Logical Device Configuration Register Definitions |     |

|       | 4.5.6. Standard Configuration Registers                           |     |

| 1     | -6. SuperI/O Configuration Registers                              |     |

|       | 4.6.1. Register Type Abbreviations                                |     |

| 4     | .7. Floppy Disk Controller (FDC) Configuration                    |     |

|       | .8. Parallel Port Configuration                                   |     |

|       | 4.8.1. Logical Device 1 (PP) Configuration                        |     |

| 4     | .9. System Wake-Up Control (SWC)                                  |     |

|       | 4.9.1. Overview                                                   |     |

|       | 4.9.2. Functional Description                                     |     |

|       | 4.9.3. Event Detection                                            |     |

|    | 4.9.4. SWC Register Bitmap                         | 291 |

|----|----------------------------------------------------|-----|

|    | 4.9.5. Keyboard/Mouse Control                      | 294 |

|    | 4.9.6. Infrared Communication Port Configuration   | 297 |

|    | 4.10. ACCESS.Bus Interface (ACB) Configuration     | 298 |

|    | 4.11. Real-time Clock (RTC)                        |     |

|    | 4.11.1. RTC Overview                               | 302 |

|    | 4.11.2. Functional Description                     | 302 |

|    | 4.11.3. RTC Configuration Registers                | 307 |

|    | 4.11.4. RTC Registers                              | 309 |

|    | 4.11.5. RTC General-purpose RAM Map                | 321 |

|    | 4.12. ACCESS.bus Interface (ACB)                   | 322 |

|    | 4.12.1. Functional Description                     | 322 |

|    | 4.12.2. ACB Registers                              | 329 |

|    | 4.13. Legacy Functional Blocks                     | 335 |

|    | 4.13.1. Keyboard and Mouse Controller (KBC)        | 335 |

|    | 4.13.2. Floppy Disk Controller (FDC)               | 336 |

|    | 4.13.3. Parallel Port                              | 337 |

|    | 4.13.4. UART Functionality (SP1/SP2)               | 340 |

|    | 4.13.5. IR Communication Port (IRCP) Functionality | 345 |

|    | ZF-Logic and Clocking                              | 403 |

| ٦. |                                                    |     |

|    | 5.1. Features                                      |     |

|    | 5.2. ZFL Register Space Summary                    |     |

|    | 5.2.1. Pins Associated with ZF-Logic               |     |

|    | 5.3. ISA Memory Mapper for Flash/SRAM              |     |

|    | 5.3.1. Window settings registers                   |     |

|    | 5.3.2. Control (R/W, 8/16)                         |     |

|    | 5.3.3. Events (SMI, etc.)                          |     |

|    | 5.3.4. Initialization of mem_cs0                   |     |

|    | 5.3.5. Sample Code for Memory Window Calculation   |     |

|    | 5.4. GPCS I/O mapper                               |     |

|    | 5.4.1. GPCS control                                |     |

|    | 5.4.2. GPCS base low byte                          |     |

|    | 5.4.3. GPCS base high byte                         |     |

|    | 5.4.4. GPCS Events                                 |     |

|    | 5.5. Watchdog Timer                                |     |

|    | 5.5.1. Watchdog Registers                          |     |

|    | 5.6. PWM generator                                 |     |

|    | 5.7. Z-tag Overview                                |     |

|    | 5.8. Boot Parameters Register                      |     |

|    | 5.8.1. Special Notes of Interest                   |     |

|    | 5.8.2. Design Example                              |     |

|    | 5.8.3. Clocking and Control Overview               |     |

|    | 5.9. Data registers (F0H to FEH)                   | 444 |

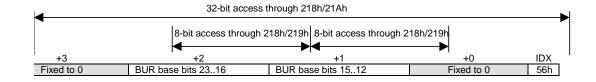

| 5.10. BUR Base Register                        | 445 |

|------------------------------------------------|-----|

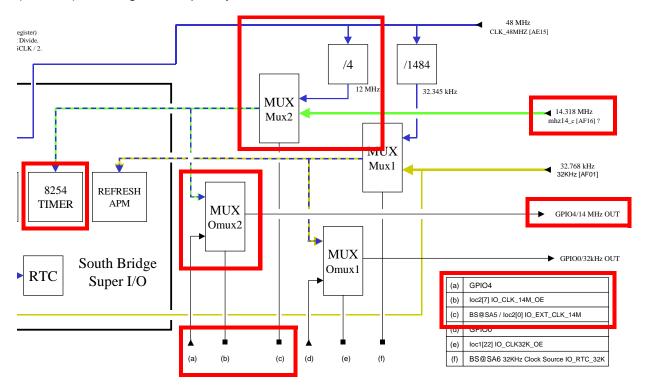

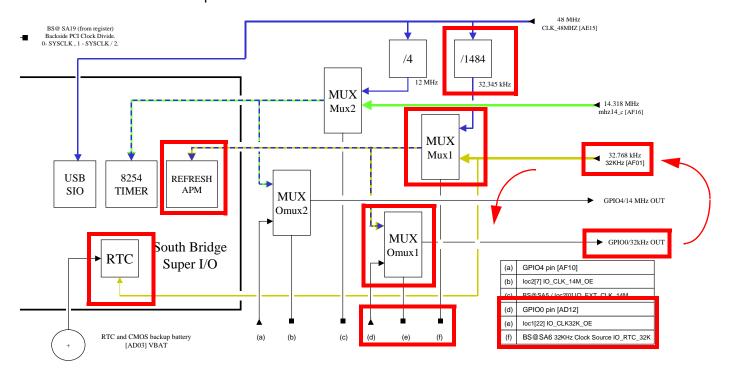

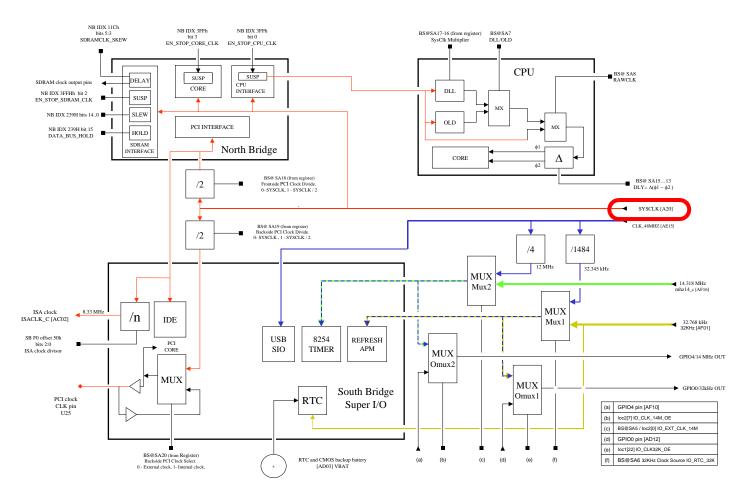

| 5.11. System Clocking                          |     |

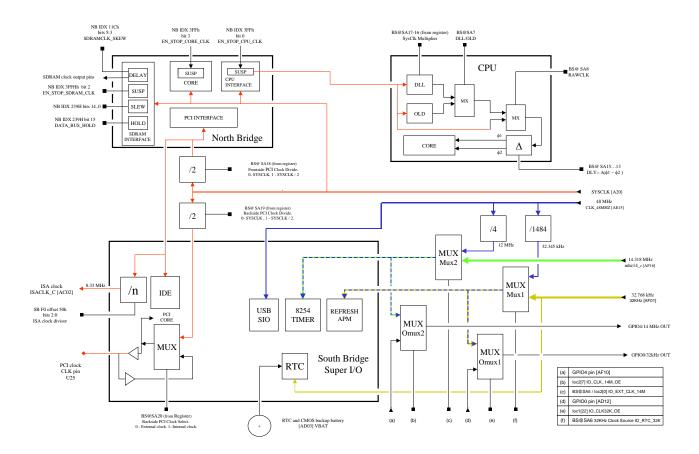

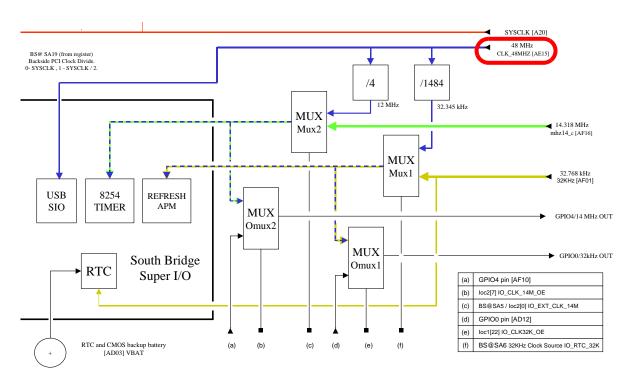

| 5.11.1. mhz_14c [AF16]                         | 448 |

| 5.11.2. 32KHZC_C [AF01]                        | 449 |

| 5.11.3. SYSCLK_C [A20]                         | 450 |

| 5.11.4. USB_48MHz_C [AE15]                     | 453 |

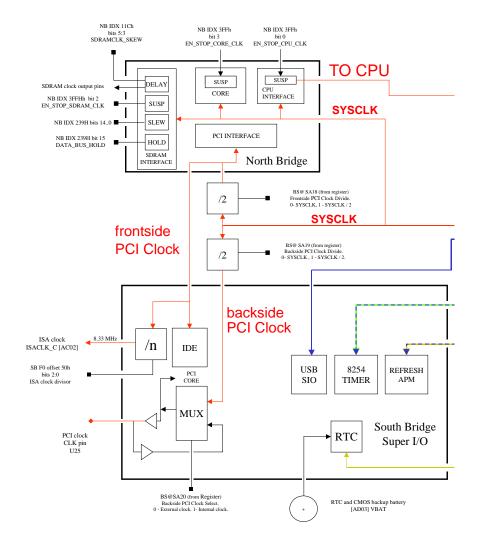

| 5.11.5. PCI Clocking                           | 454 |

| 6. Z-tag, BUR, and The ZFiX Console            | 455 |

| 6.1. Serial Port Connection                    | 455 |

| 6.2. Z-Tag Dongles                             |     |

| 6.2.1. PassThrough Dongle                      | 455 |

| 6.2.2. Memory Dongle                           | 455 |

| 6.2.3. Using the Dongle                        | 456 |

| 6.3. Z-tag Manager Software                    |     |

| 6.3.1. Z-tag Summary                           | 459 |

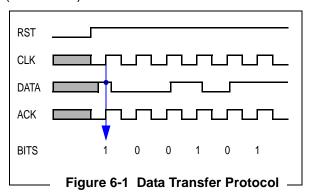

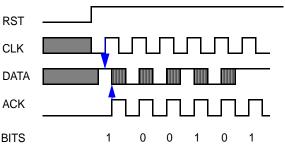

| 6.3.2. Z-tag Data Transfer Protocol            | 460 |

| 6.3.3. Z-tag Port Interface                    |     |

| 6.4. Z-tag Register Descriptions               |     |

| 6.4.1. Z-tag Data (D1h)                        |     |

| 6.4.2. Z-tag Control (7Ch)                     | 461 |

| 6.5. BUR (Boot Up ROM)                         |     |

| 6.5.1. ZFiX Console Functions                  |     |

| 6.5.2. Z-tag Functionality                     |     |

| 6.5.3. Internal Functionality                  |     |

| 6.6. BUR COM1 Download Examples                |     |

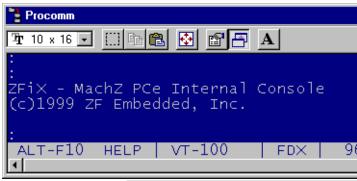

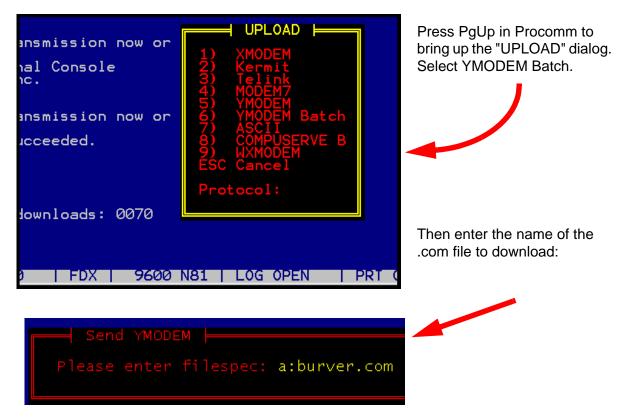

| 6.6.1. Procomm: Download a Test Program        |     |

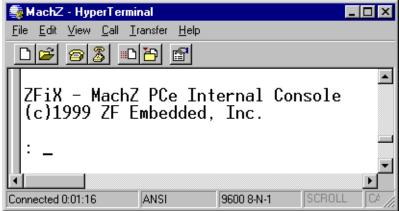

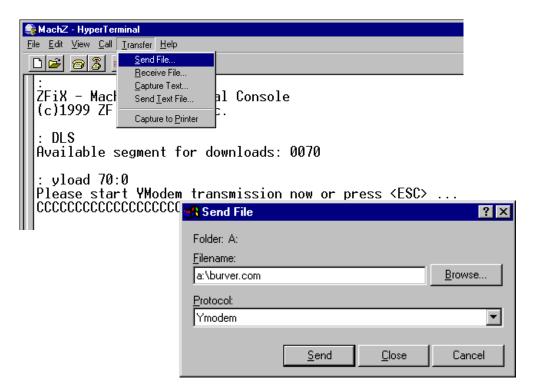

| 6.6.2. HyperTerminal: Download a Test Program  |     |

| 6.6.3. BUR Version Test Program Source Code    |     |

| 6.6.4. BUR/BET Memory Map                      |     |

| 6.7. Flash Programming Example                 | 470 |

| 7. Electrical Specifications                   | 481 |

| 7.1. General Specifications                    | 481 |

| 7.1.1. MTTF and FIT Specifications             | 481 |

| 7.1.2. Power/Ground Connections and Decoupling | 481 |

| 7.2. Signal I/O Buffer Type Directory          | 483 |

| 7.3. Detailed DC Characteristics of Cells      |     |

| 7.4. AC Characteristics                        | 489 |

| 7.4.1. System Interface                        | 489 |

| 7.4.2. Memory Interface                        |     |

| 7.4.3. ACCESS.bus Interface                    | 494 |

| 7.4.4. PCI Bus                                 | 495 |

| 7.4.5. ISA Interface                           |     |

| 7.4.6. IDE Interface Timing                    | 504 |

|             | 7.4.7. Universal Serial Bus (USB)                        | 523         |

|-------------|----------------------------------------------------------|-------------|

|             | 7.4.8. Serial Port (UART)                                | 527         |

|             | 7.4.9. Fast IR Port Timing                               | 528         |

|             | 7.4.10. JTAG Timing                                      | 529         |

|             | 7.4.11. GPIO Timing                                      | 530         |

|             | 7.4.12. Floppy Disk Interface                            | 531         |

|             | 7.4.13. Keyboard and Mouse Interface                     | 533         |

|             | 7.4.14. Parallel Port                                    | 534         |

|             | 7.4.15. ZF-Logic                                         | <b>5</b> 40 |

| <b>8.</b> l | Pinout Summary                                           | . 541       |

|             | 8.1. Pad Assignments                                     | 541         |

|             | 8.2. Pin Descriptions (Sorted by Pin)                    |             |

|             | 8.3. Pin Descriptions (Sorted by Pin Name)               |             |

|             | 8.4. Pin Descriptions (Sorted by Pin Description)        |             |

| <b>9.</b>   | BUR API                                                  | . 587       |

|             | 9.1. Using the BUR API                                   | 587         |

|             | 9.2. Function Call Definitions                           |             |

| 10          | . Signal Status After POST                               |             |

|             | _                                                        |             |

|             | 10.1. Access Bus                                         |             |

|             | 10.2. Floppy Disk                                        |             |

|             | 10.2.2. Z-tag Active                                     |             |

|             | 10.3. GPIO                                               |             |

|             | 10.4. ISA                                                |             |

|             | 10.5. PS/2                                               |             |

|             | 10.6. PCI                                                |             |

|             | 10.7. LPT                                                |             |

|             | 10.8. IR Control (COM2)                                  | . 601       |

|             | 10.9. ZF Logic                                           | . 601       |

| 11.         | Phoenix BIOS Register Settings                           | . 603       |

|             | 11.1. North Bridge                                       | . 603       |

|             | 11.1.1. Reset, Sampling, and Misc North Bridge Registers |             |

|             | 11.1.2. DRAM Registers                                   |             |

|             | 11.1.3. Power Management Registers                       |             |

|             | 11.1.4. PCI Configuration Registers                      |             |

|             | 11.2. South Bridge                                       |             |

|             | 11.2.1. Floppy Disk Controller                           |             |

|             | 11.2.2. Parallel Port                                    | 629         |

|             | 11.2.3. Serial Port 1                                    | 630         |

|             | 11.2.4. Serial Port 2                                    | 632         |

|             | 11.2.5. PS/2 Mouse/Keyboard                              |             |

|             | 11.2.6. Infrared Communication Port Configuration        | 635         |

|             |                                                          |             |

| Index |                                   | 653 |

|-------|-----------------------------------|-----|

|       | 11.2.9. GPIO Configuration Pins   | 640 |

|       | ·                                 |     |

|       | 11.2.8. Pin Multiplexor Registers | 637 |

|       | 11.2.7. Access Bus                | 636 |

| <b>Table of Cont</b> | ents                                       | 7   |

|----------------------|--------------------------------------------|-----|

| List of Figure       | s                                          | 13  |

| List of Tables       | ;                                          | 17  |

| 1. Overview          |                                            | 29  |

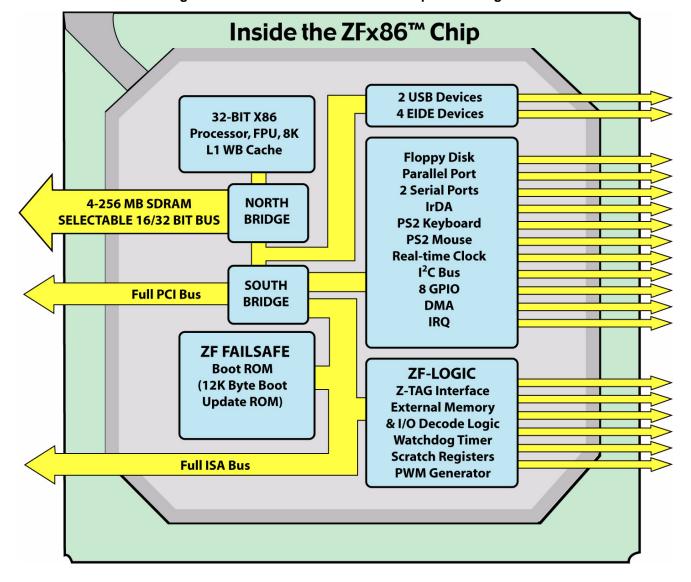

| Figure 1-1           | ZFx86 Fail-Safe PC-on-a-Chip Block Diagram | 30  |

| 2. 32-bit x86 P      | rocessor                                   | 31  |

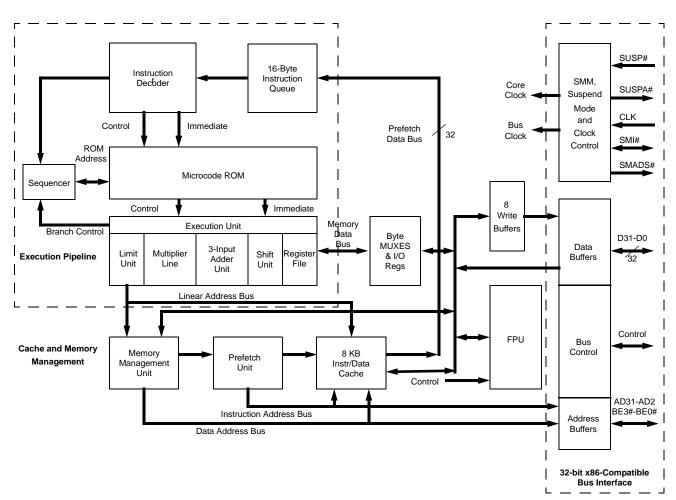

| Figure 2-1           | Processor Block Diagram                    | 31  |

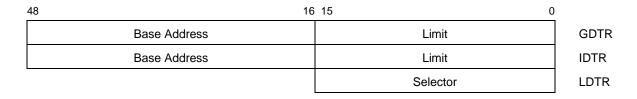

| Figure 2-2           | Task Register                              | 46  |

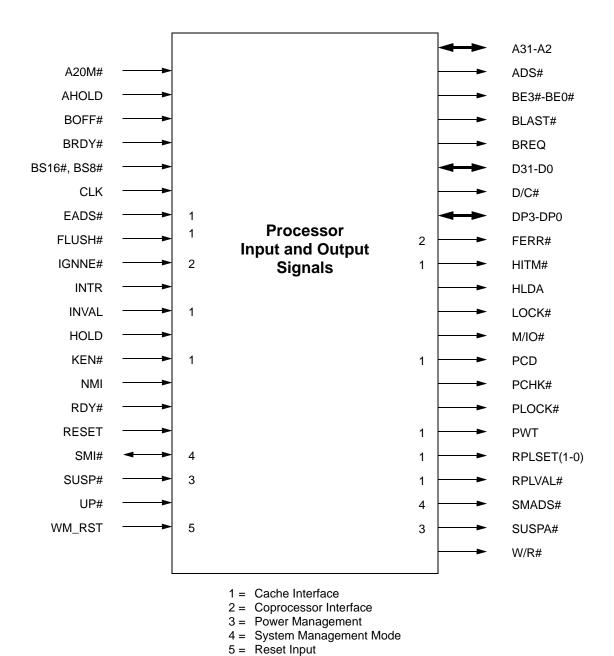

| Figure 2-3           | Processor Internal I/O Interface Signals   |     |

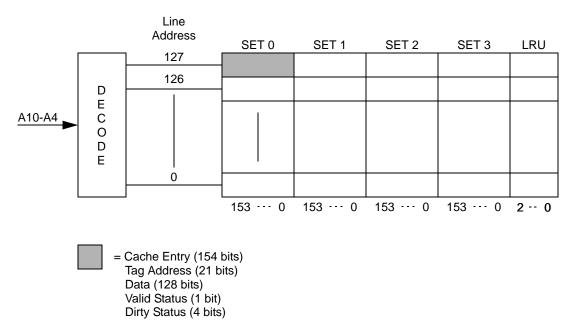

| Figure 2-4           | Processor Cache Architecture               |     |

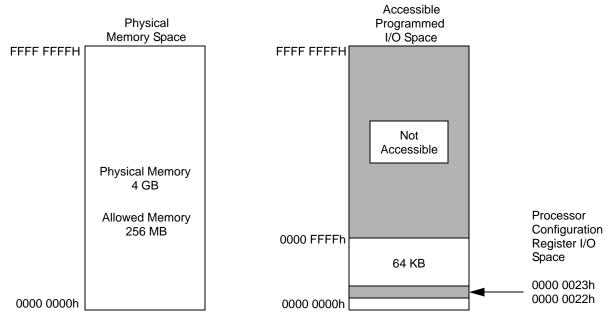

| Figure 2-5           | Memory and I/O Address Spaces              |     |

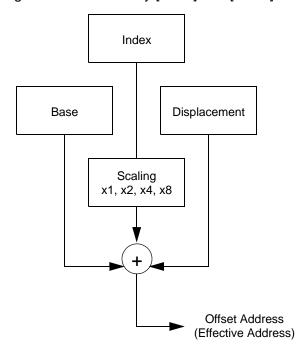

| Figure 2-6           | Offset Address Calculation                 |     |

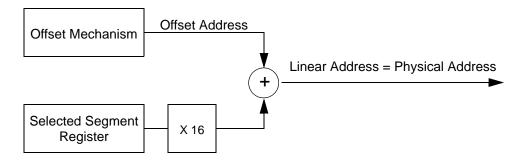

| Figure 2-7           | Real Mode Address Calculation              |     |

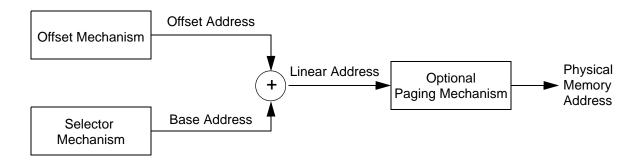

| Figure 2-8           | Protected Mode Address Calculation         |     |

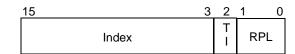

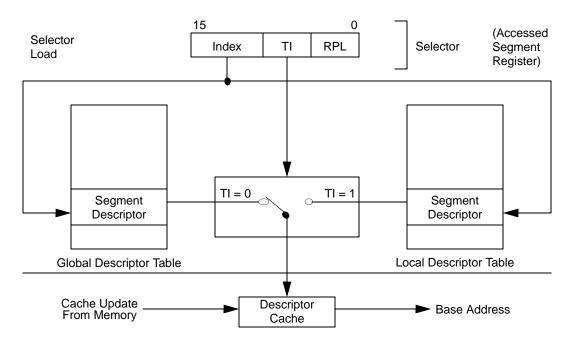

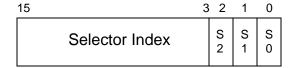

| Figure 2-9           | Selector Mechanism                         | 64  |

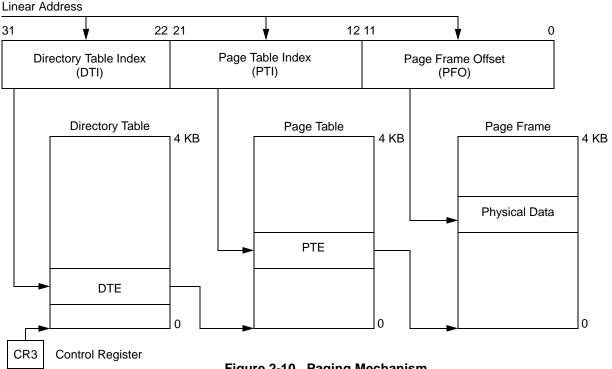

| Figure 2-10          | Paging Mechanism                           |     |

| Figure 2-11          | Error Code Format                          |     |

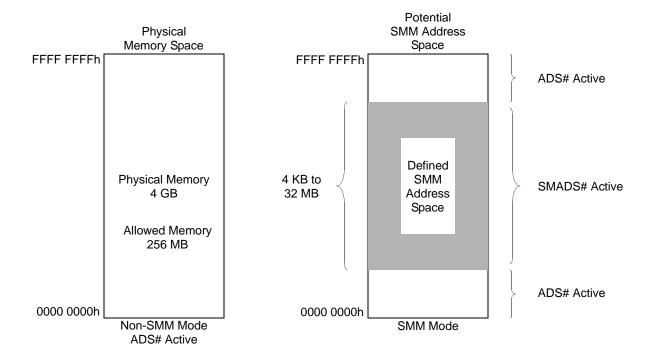

| Figure 2-12          | System Management Memory Address Space     | 72  |

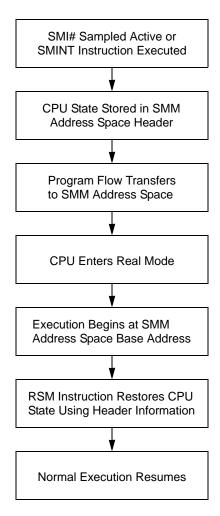

| Figure 2-13          | SMI Execution Flow Diagram                 |     |

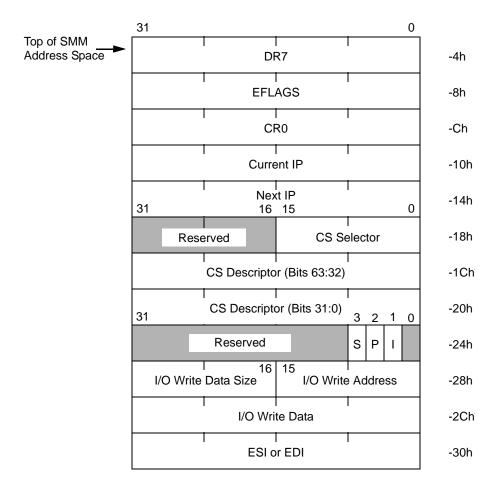

| Figure 2-14          | SMM Memory Space Header                    | 74  |

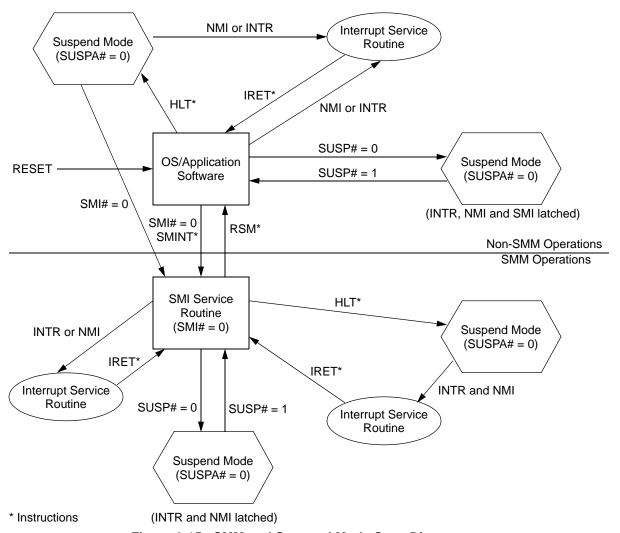

| Figure 2-15          | SMM and Suspend Mode State Diagram         |     |

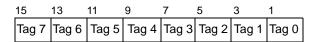

| Figure 2-16          | Tag Word Register                          | 84  |

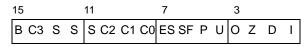

| Figure 2-17          | FPU Status Register                        | 84  |

| Figure 2-18          | FPU Mode Control Register                  | 84  |

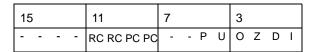

| Figure 2-19          | Instruction Set Format                     | 86  |

| 3. North Bridg       | e                                          | 113 |

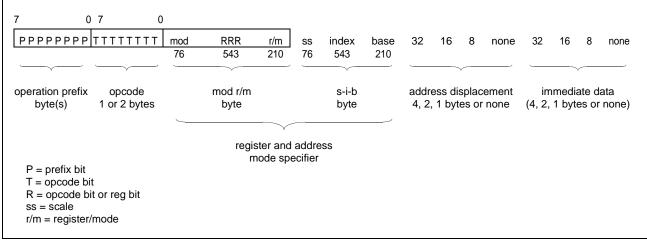

| Figure 3-1           | Data Paths                                 | 114 |

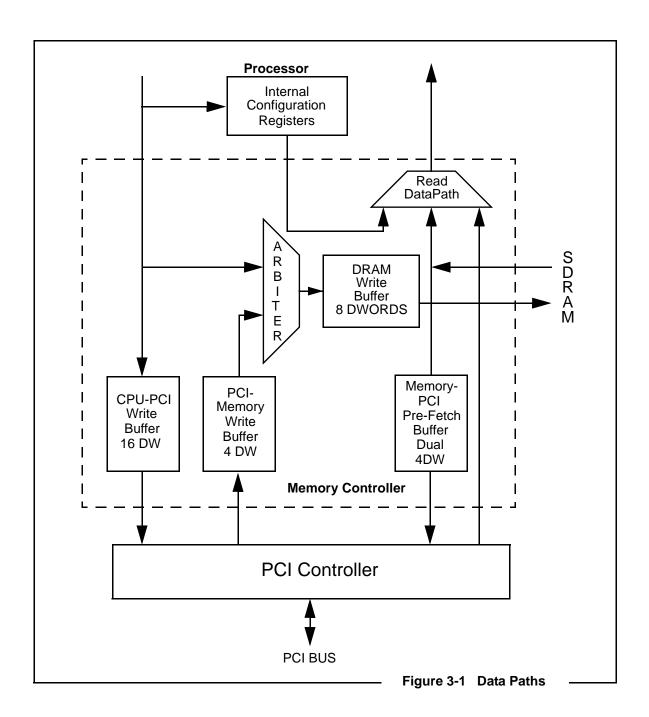

| Figure 3-2           | Block Diagram                              |     |

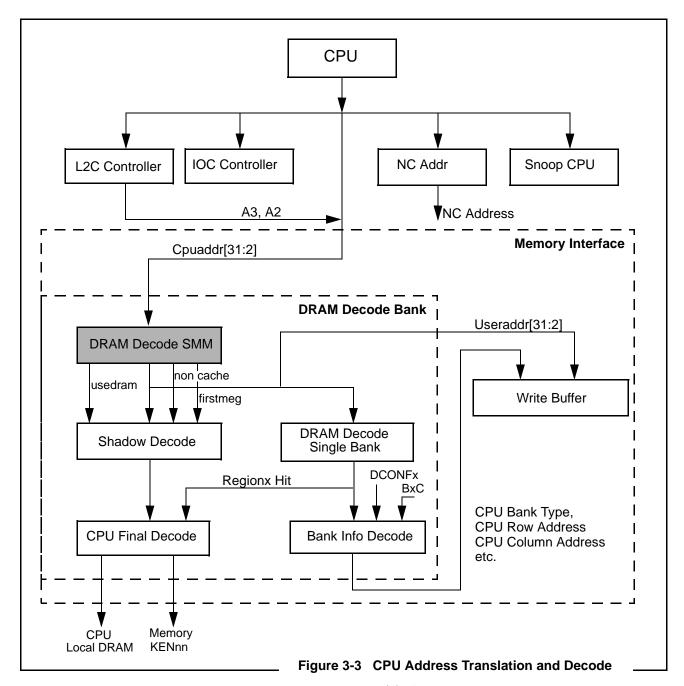

| Figure 3-3           | CPU Address Translation and Decode         | 122 |

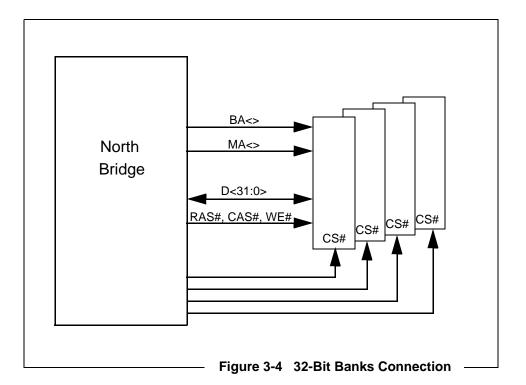

| Figure 3-4           | 32-Bit Banks Connection                    |     |

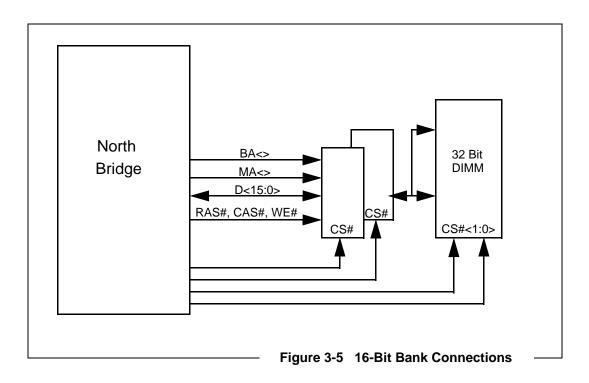

| Figure 3-5           | 16-Bit Bank Connections                    |     |

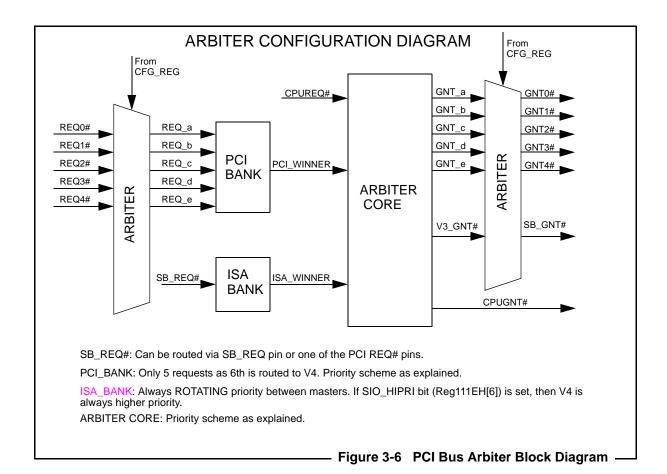

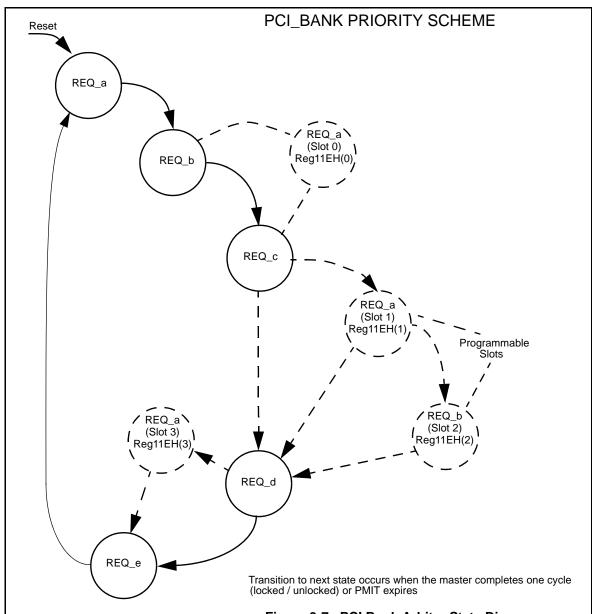

| Figure 3-6           | PCI Bus Arbiter Block Diagram              | 128 |

| Figure 3-7           | PCI Bank Arbiter State Diagram             |     |

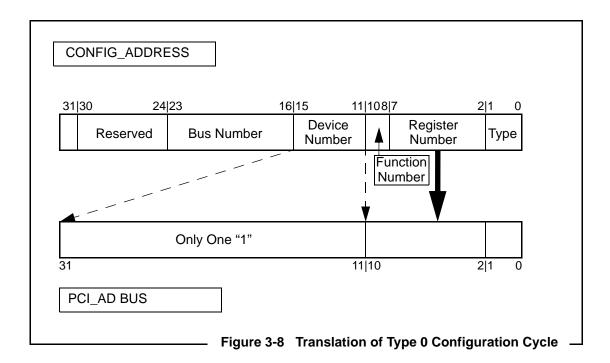

| Figure 3-8           | Translation of Type 0 Configuration Cycle  | 132 |

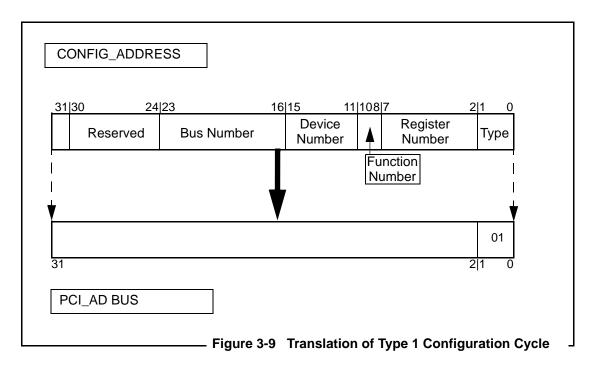

| Figure 3-9           | Translation of Type 1 Configuration Cycle  | 132 |

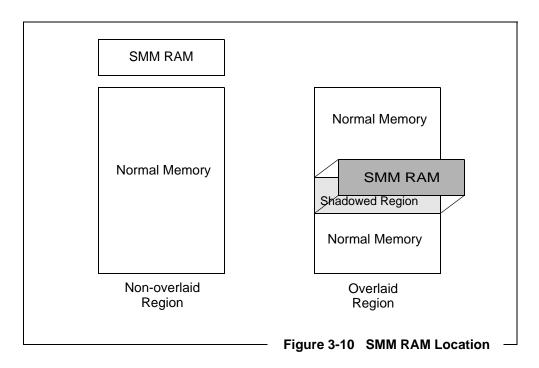

| Figure 3-10          | SMM RAM Location                           | 135 |

| 4. South Bridg       | ge                                         | 165 |

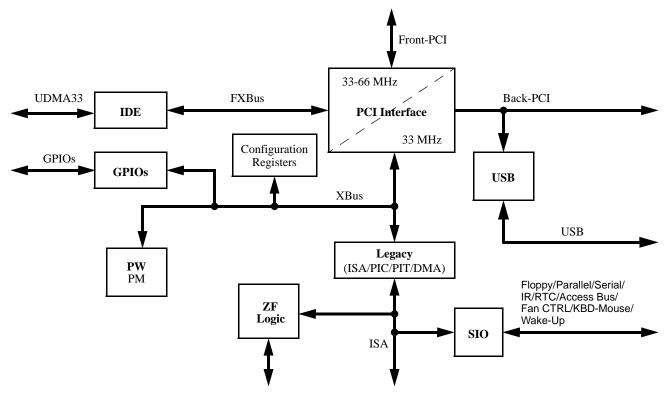

| Figure 4-1           | Internal Block Diagram                     | 167 |

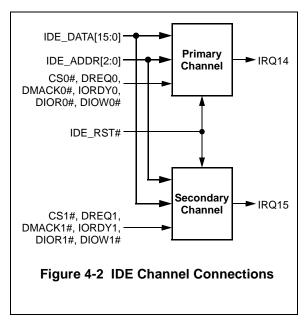

| Figure 4-2           | IDE Channel Connections                    | 168 |

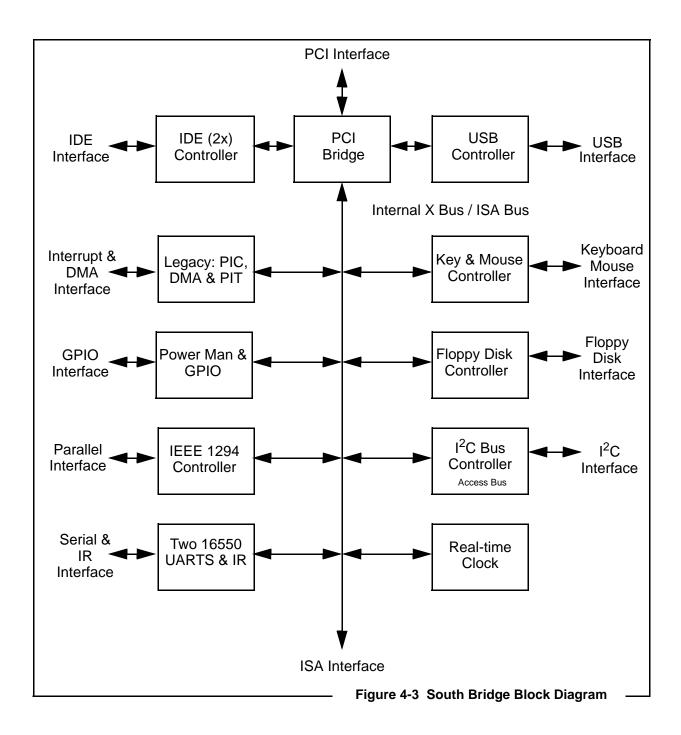

| Figure 4-3           | South Bridge Block Diagram                 | 172 |

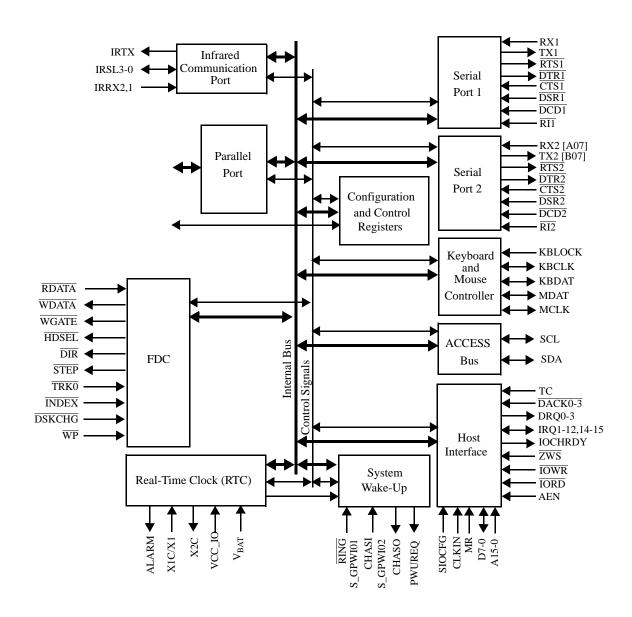

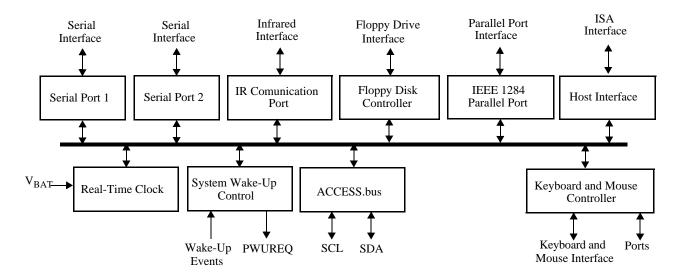

| Figure 4-4           | Super I/O Block Diagram                    | 259 |

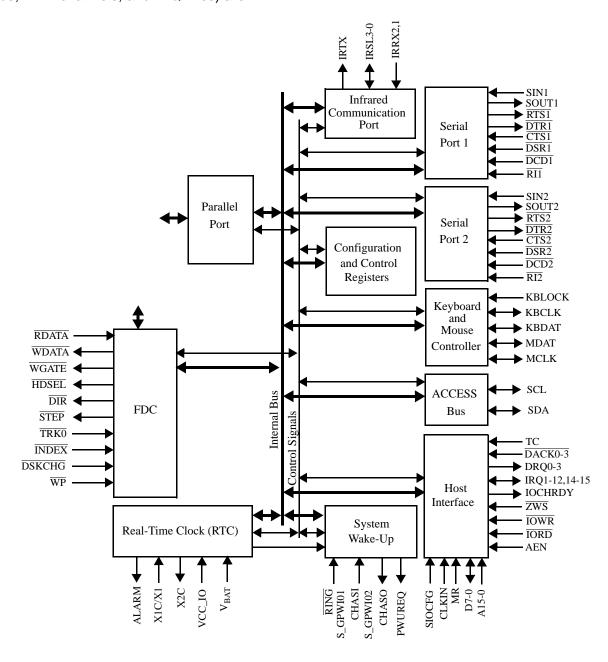

| Figure 4-5     | Detailed SuperI/O Block Diagram                             | 262 |

|----------------|-------------------------------------------------------------|-----|

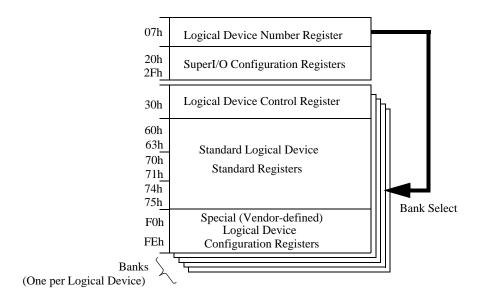

| Figure 4-6     | Structure of the Standard Configuration Register File       |     |

| Figure 4-7     | Configuration Register Map                                  |     |

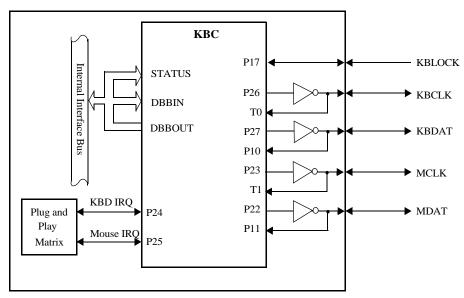

| Figure 4-8     | Keyboard and Mouse Interfaces                               | 295 |

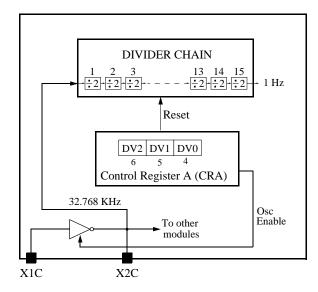

| Figure 4-9     | Divider Chain Control                                       | 303 |

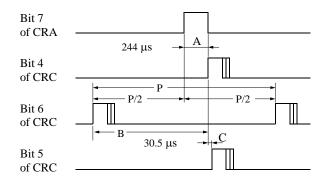

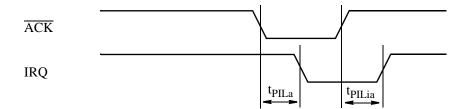

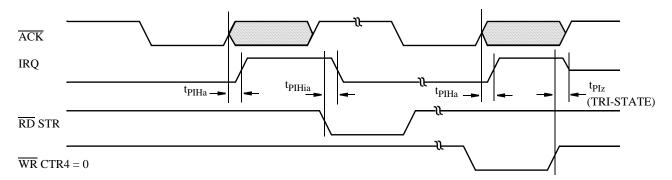

| Figure 4-10    | Interrupt/Status Timing                                     | 306 |

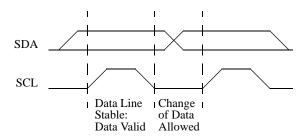

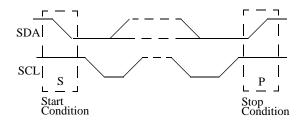

| Figure 4-11    | Bit Transfer                                                | 323 |

| Figure 4-12    | Start and Stop Conditions                                   | 323 |

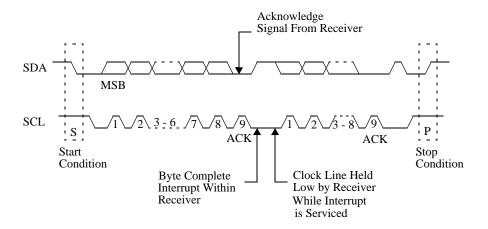

| Figure 4-13    | ACCESS.bus Data Transaction                                 | 323 |

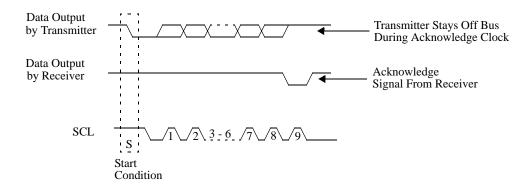

| Figure 4-14    | ACCESS.bus Acknowledge Cycle                                | 324 |

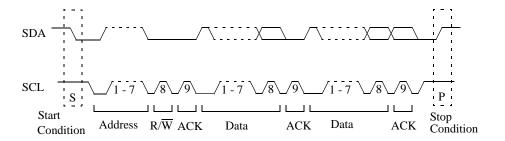

| Figure 4-15    | A Complete ACCESS.bus Data Transaction                      | 325 |

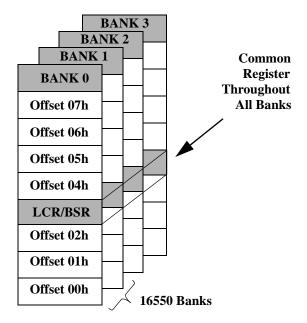

| Figure 4-16    | UART Mode Register Bank Architecture                        | 341 |

| Figure 4-17    | Composite Serial Data                                       |     |

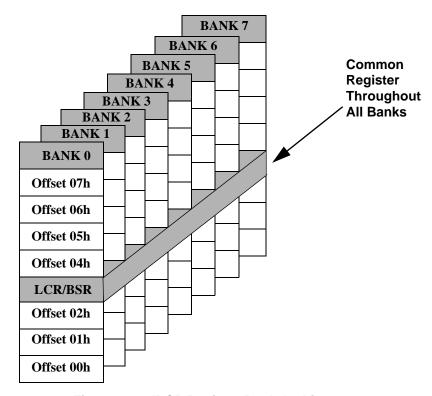

| Figure 4-18    | IRCP Register Bank Architecture                             | 355 |

| Figure 4-19    | DMA Control Signals Routing                                 | 377 |

| 5. ZF-Logic ar | nd Clocking                                                 | 403 |

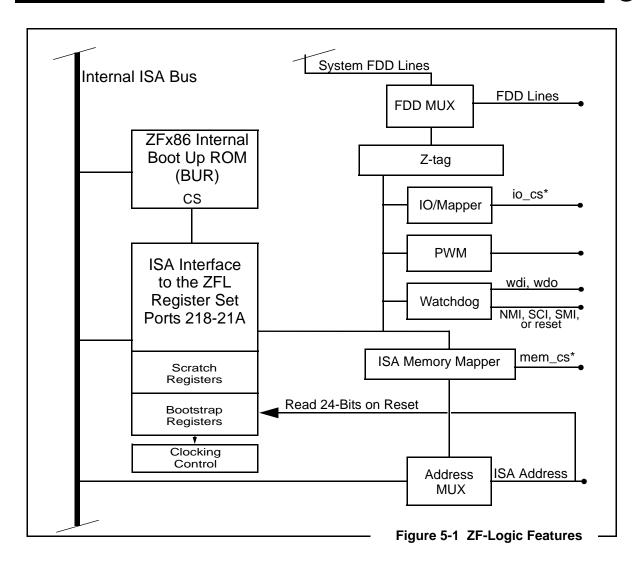

| Figure 5-1     | ZF-Logic Features                                           | 404 |

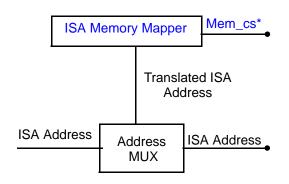

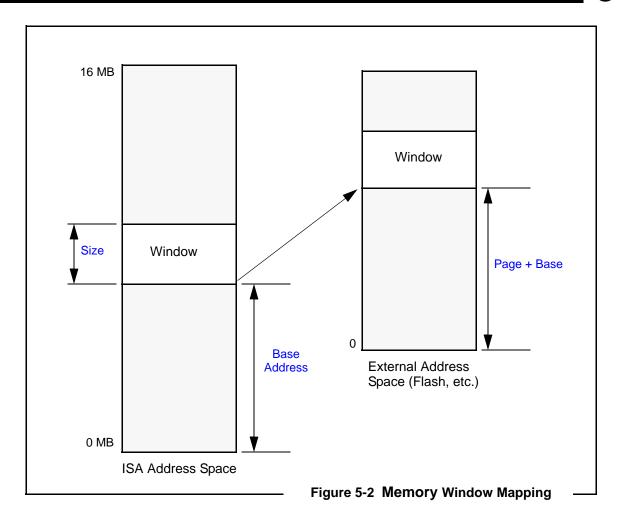

| Figure 5-2     | Memory Window Mapping                                       |     |

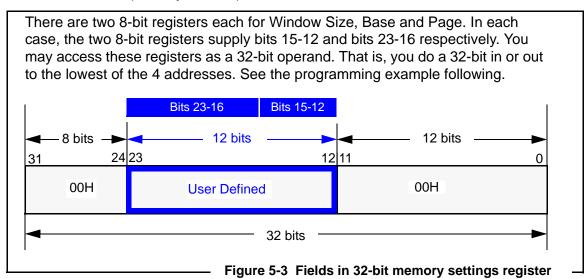

| Figure 5-3     | Fields in 32-bit memory settings register                   |     |

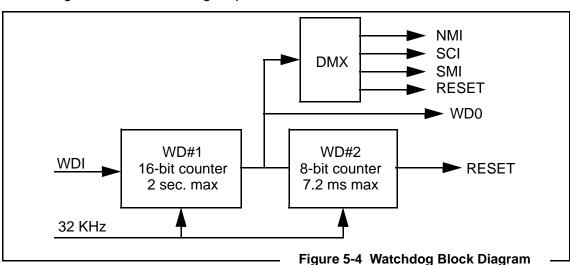

| Figure 5-4     | Watchdog Block Diagram                                      |     |

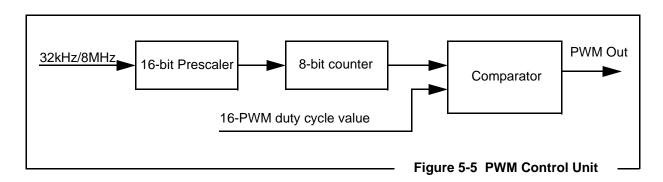

| Figure 5-5     | PWM Control Unit                                            |     |

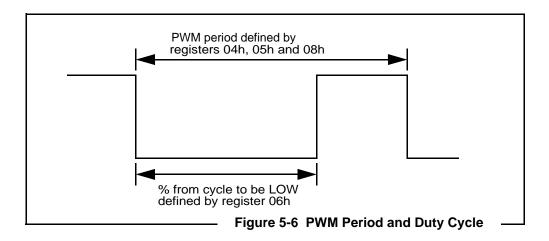

| Figure 5-6     | PWM Period and Duty Cycle                                   |     |

| Figure 5-7     | Dongle (w/o Cover)                                          |     |

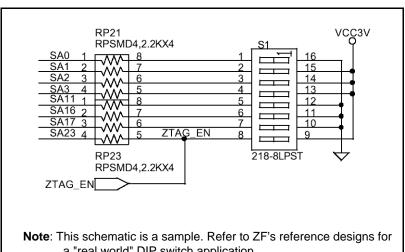

| Figure 5-8     | Sample DIP Switch Schematic                                 |     |

| Figure 5-9     | System Clocking and Control                                 |     |

| Figure 5-10    | mhz_14c[AF16] Clocking Control Circuitry                    |     |

| Figure 5-11    | 32KHZC_C [AF01] Clocking Control Circuitry                  |     |

| Figure 5-12    | SYSCLK_C [A20] Clocking Control Circuitry                   |     |

| Figure 5-13    | USB_48MHz_C [AE15] Clocking Control Circuitry               |     |

| Figure 5-14    | PCI Clocking Control Circuitry                              |     |

| 6. Z-tag. BUR. | and The ZFiX Console                                        | 455 |

| Figure 6-1     | Data Transfer Protocol                                      |     |

| Figure 6-2     | Data Input                                                  | 400 |

| Figure 6-3     | Dongle Data Record                                          |     |

| Figure 6-4     | Using Procomm YMODEM Batch                                  |     |

| Figure 6-5     | Using HyperTerminal - Send File Ymodem                      |     |

|                | pecifications                                               |     |

|                |                                                             |     |

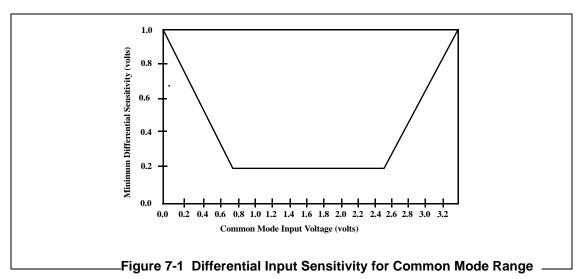

| Figure 7-1     | Differential Input Sensitivity for Common Mode Range        |     |

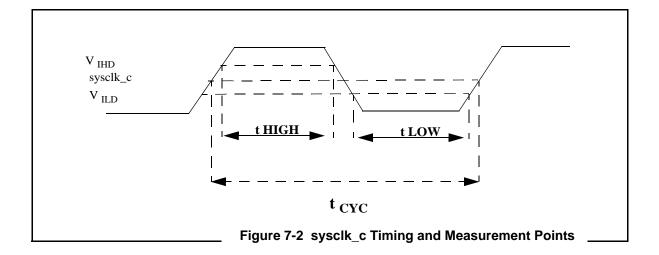

| Figure 7-2     | sysclk_c Timing and Measurement Points                      |     |

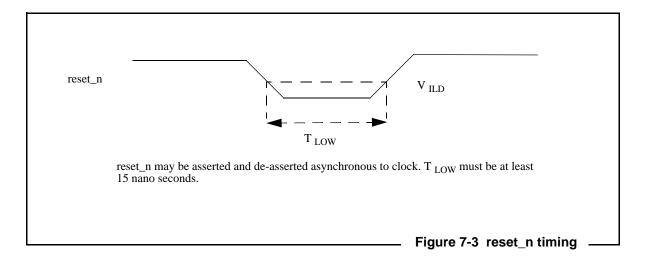

| Figure 7-3     | reset_n timing                                              |     |

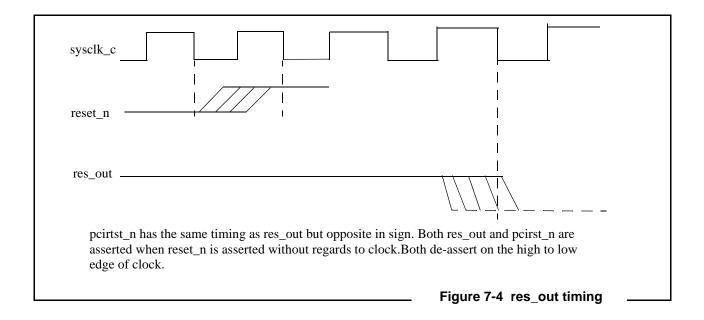

| Figure 7-4     | res_out timing                                              |     |

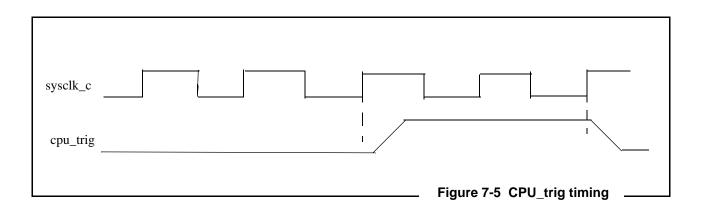

| Figure 7-5     | CPU_trig timing                                             |     |

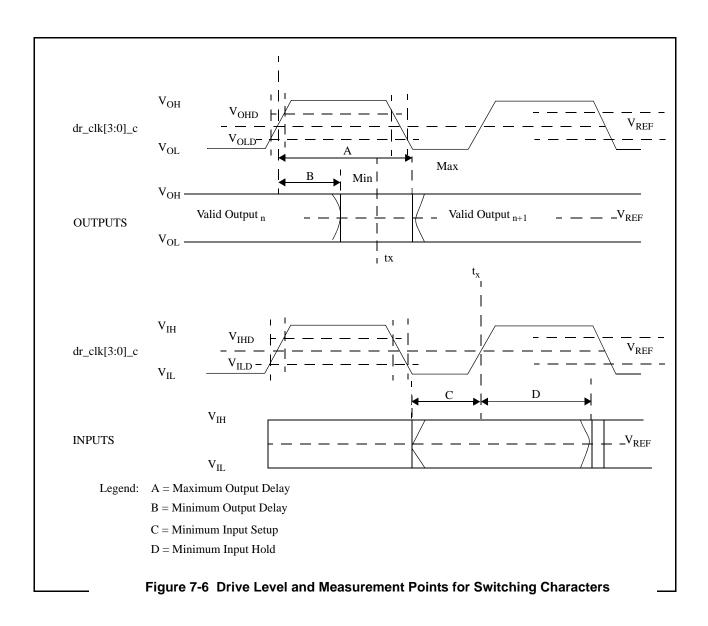

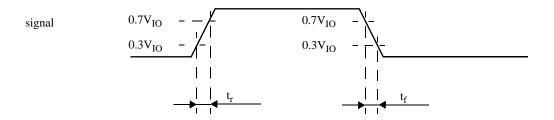

| Figure 7-6     | Drive Level and Measurement Points for Switching Characters |     |

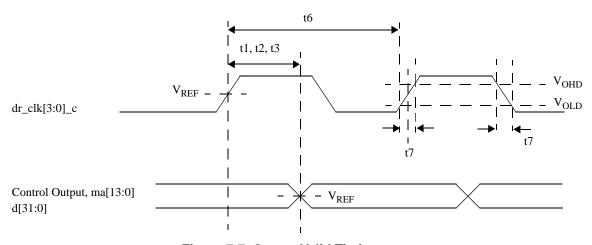

| Figure 7-7     | Output Valid Timing                                         | 493 |

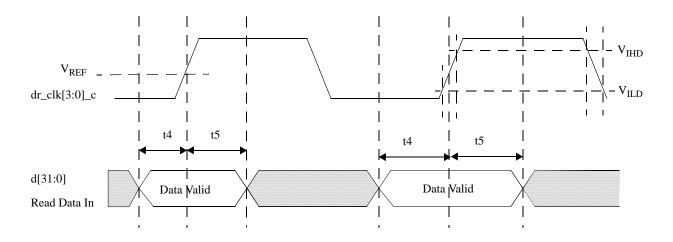

| Figure 7-8  | Setup and Hold Timing - Read Data In                    | 494 |

|-------------|---------------------------------------------------------|-----|

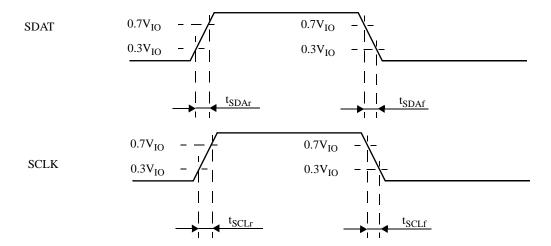

| Figure 7-9  | ACB Signals (SDAT AND SCLK) Rising and Falling times    | 494 |

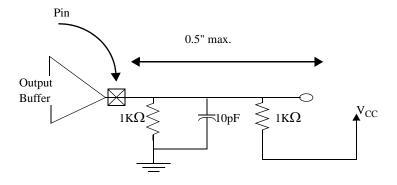

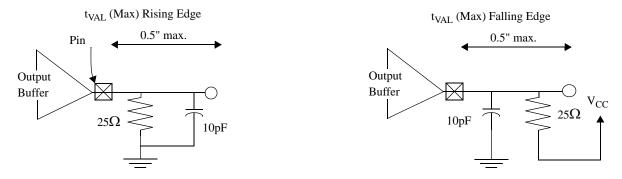

| Figure 7-10 | Testing Setup for Slew Rate and Minimum Timing          | 496 |

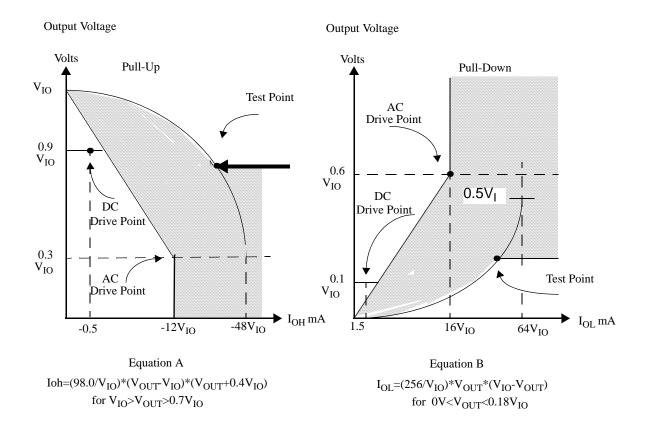

| Figure 7-11 | V/I Curves for PCI Output Signals                       | 496 |

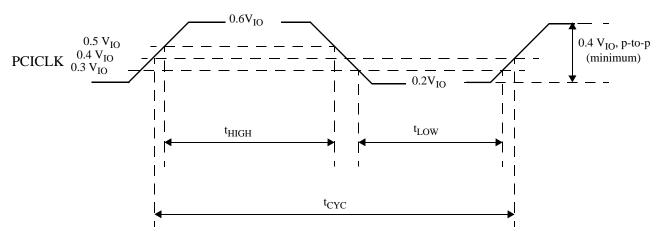

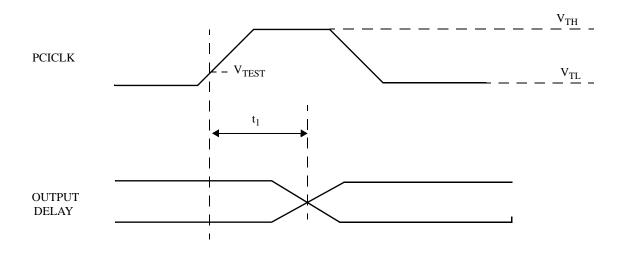

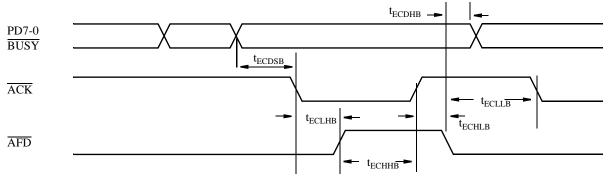

| Figure 7-12 | PCICLK Timing and Measurement Points                    | 497 |

| Figure 7-13 | Load Circuits for Maximum Time Measurements             | 498 |

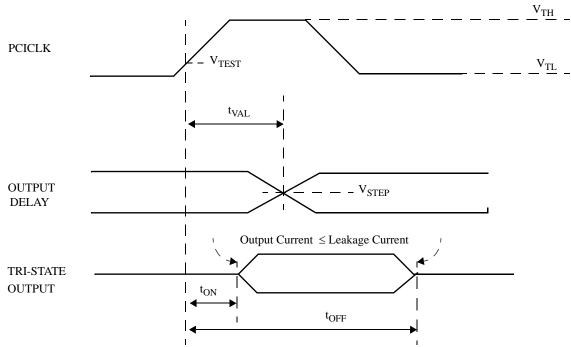

| Figure 7-14 | Output Timing Measurement Conditions                    | 499 |

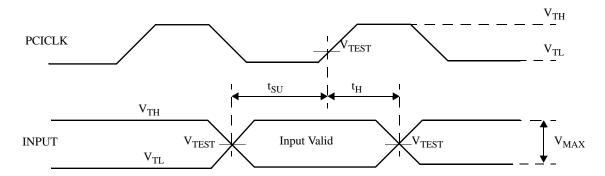

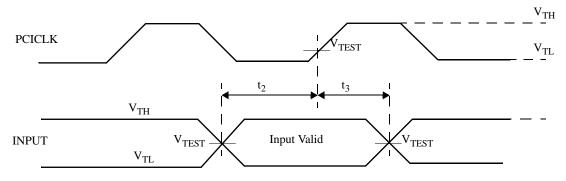

| Figure 7-15 | Input Timing Measurement Conditions                     | 500 |

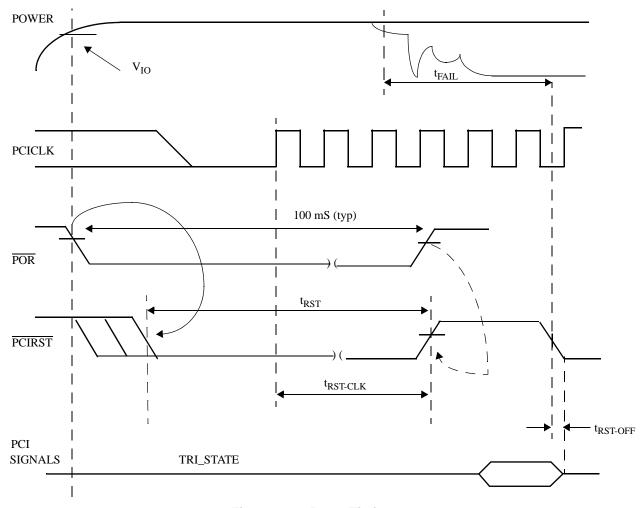

| Figure 7-16 | Reset Timing                                            | 500 |

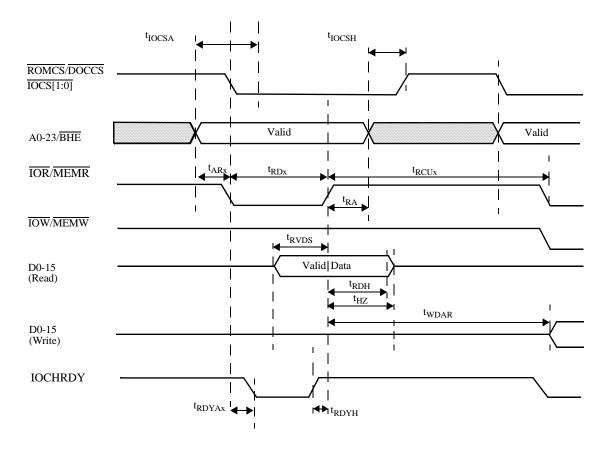

| Figure 7-17 | ISA Read Operation                                      | 503 |

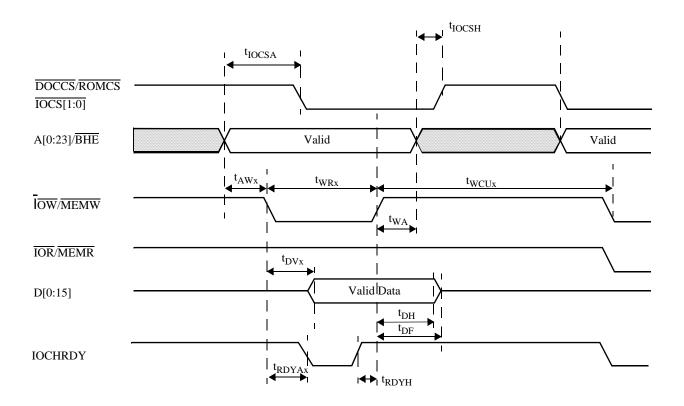

| Figure 7-18 | ISA Write Operation                                     | 503 |

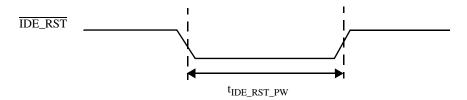

| Figure 7-19 | IDE Reset Timing                                        | 504 |

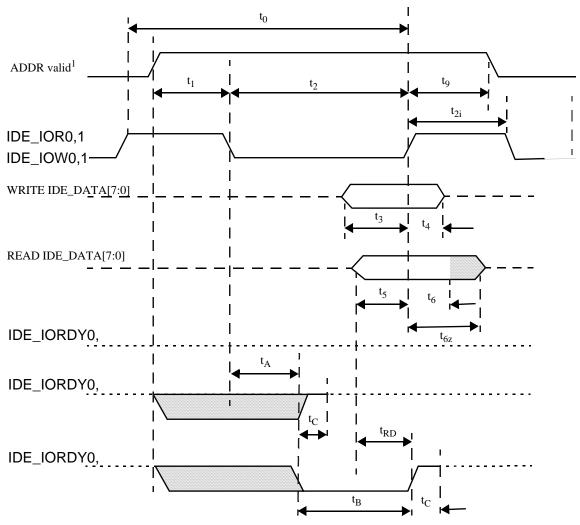

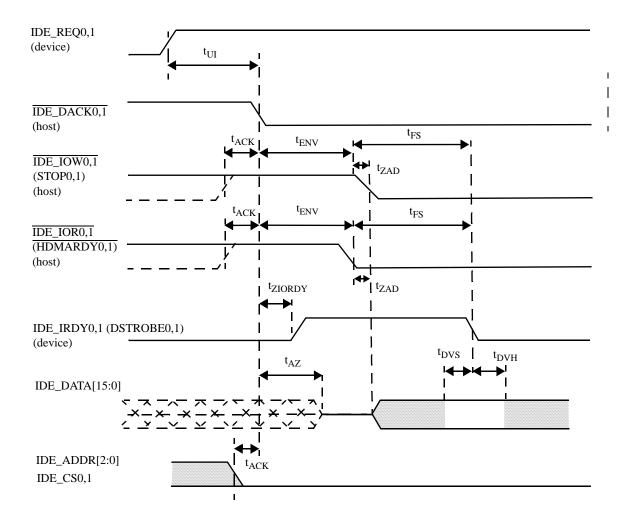

| Figure 7-20 | IDE Register Transfer To/From Device                    | 506 |

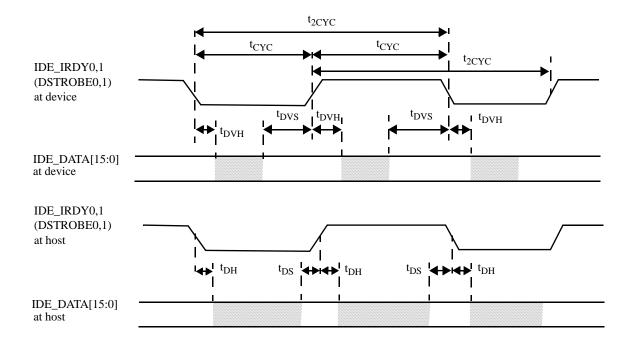

| Figure 7-21 | IDE PIO Data Transfer To/From Device                    |     |

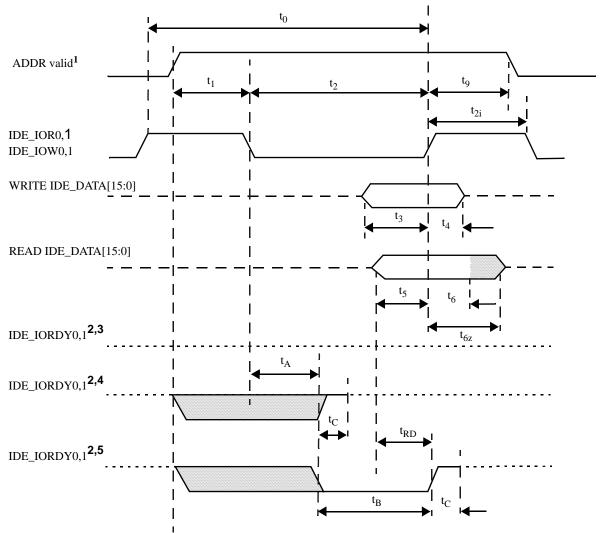

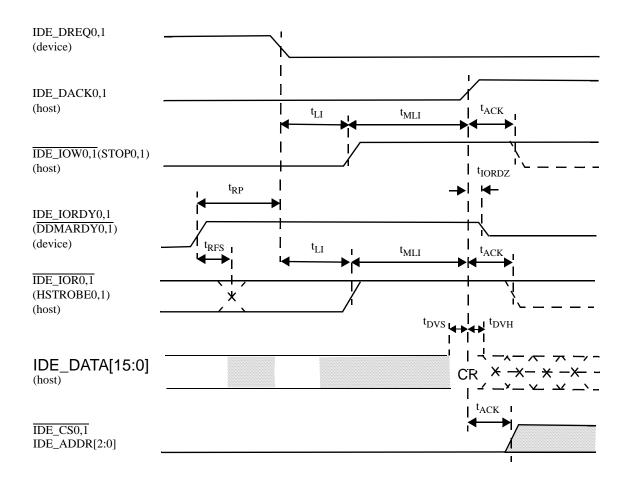

| Figure 7-22 | Multiword Data Transfer                                 | 510 |

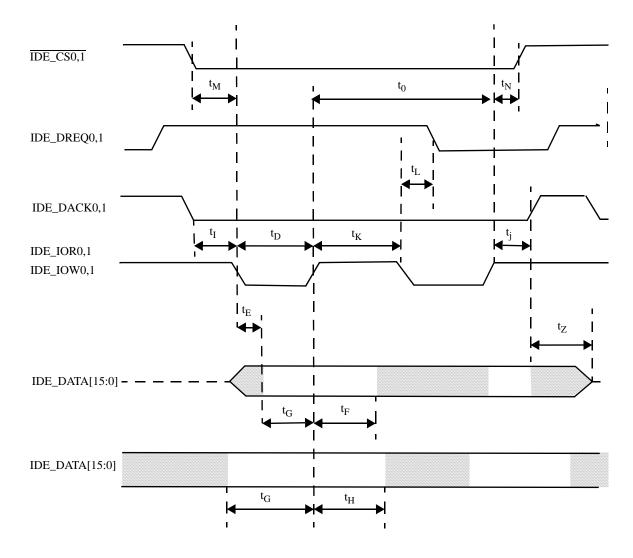

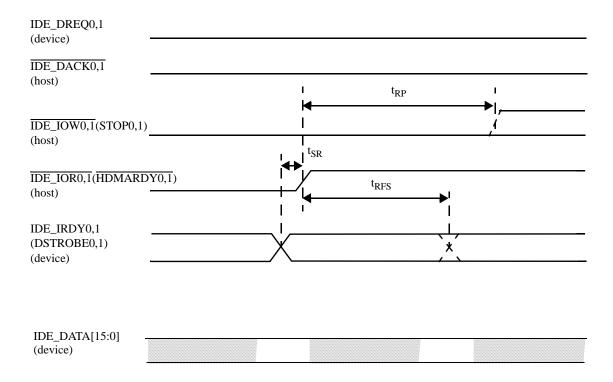

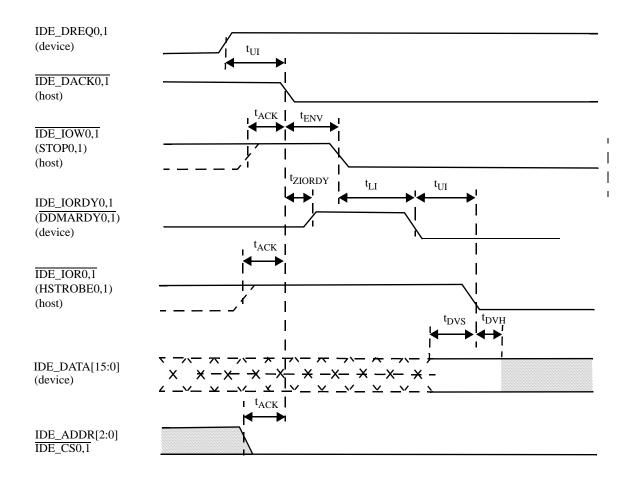

| Figure 7-23 | Initiating an Ultra DMA Data in Burst                   | 513 |

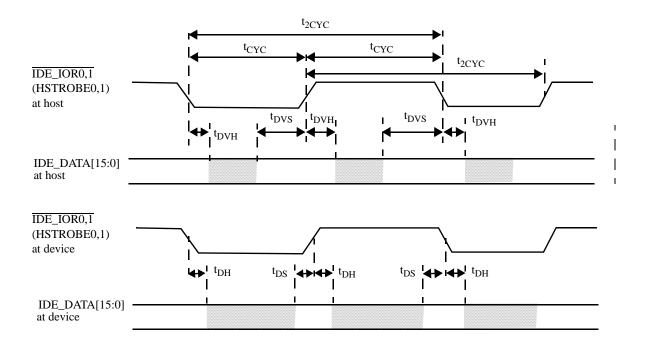

| Figure 7-24 | Sustained Ultra DMA Data In Burst                       | 514 |

| Figure 7-25 | Host Pausing an Ultra DMA Data In Burst                 | 515 |

| Figure 7-26 | Device Terminating an Ultra DMA Data In Burst           |     |

| Figure 7-27 | Host Terminating an Ultra DMA Data In Burst             |     |

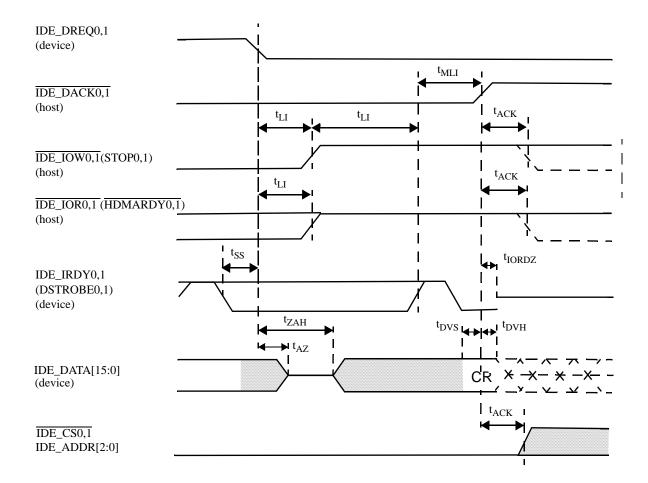

| Figure 7-28 | Initiating an Ultra DMA Data Out Burst                  |     |

| Figure 7-29 | Sustained Ultra DMA Data Out Burst                      |     |

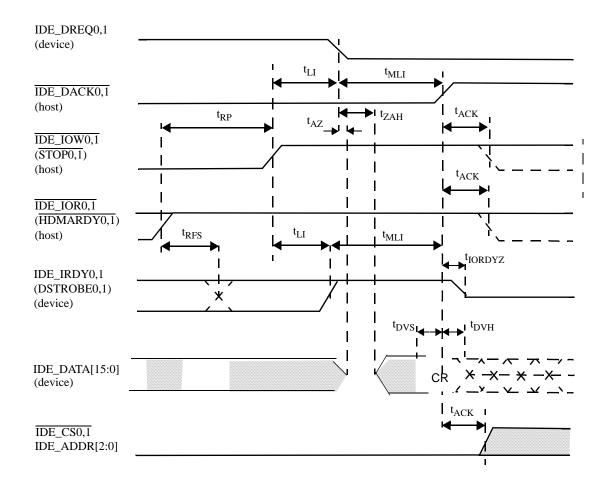

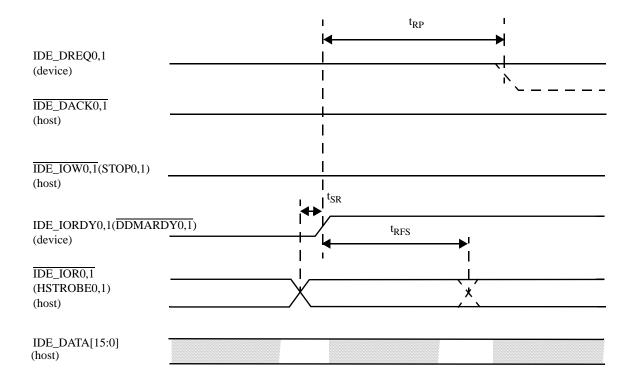

| Figure 7-30 | Device Pausing an Ultra DMA Data Out Burst              | 520 |

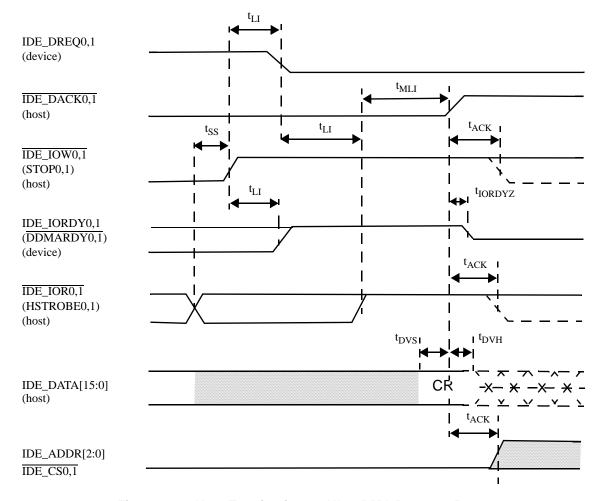

| Figure 7-31 | Host Terminating an Ultra DMA Data Out Burst            |     |

| Figure 7-32 | Device Terminating an Ultra DMA Data Out Burst          |     |

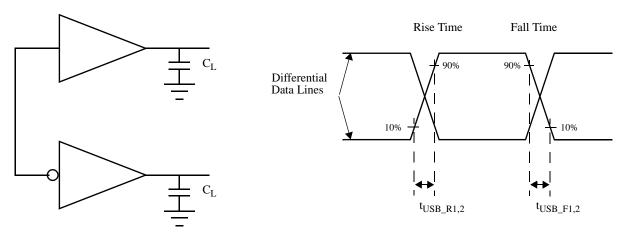

| Figure 7-33 | Data Signal Rise and Fall Time                          |     |

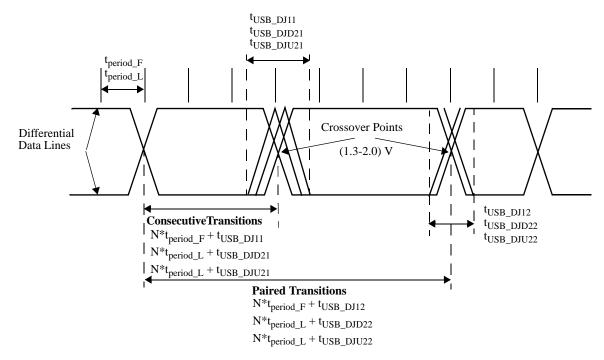

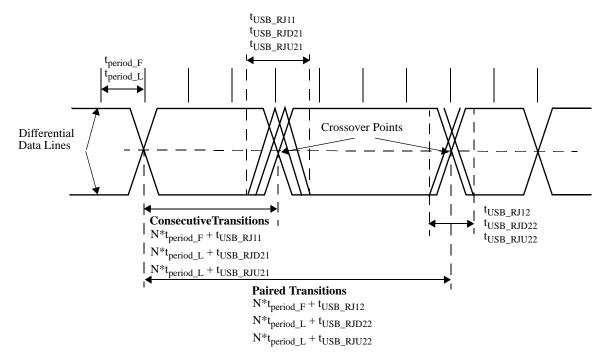

| Figure 7-34 | Source Differential Data Jitter                         |     |

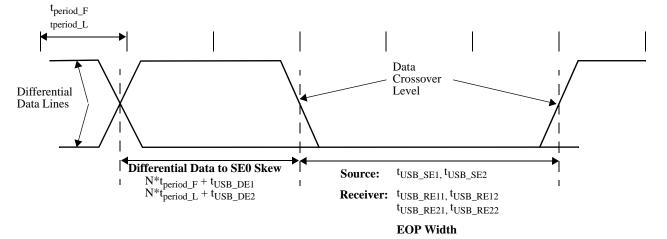

| Figure 7-35 | EOP Width Timing                                        |     |

| Figure 7-36 | Receiver Jitter Tolerance                               |     |

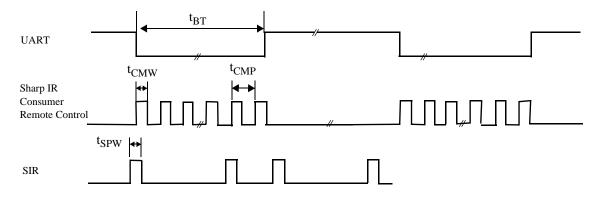

| Figure 7-37 | UART, Sharp-IR, SIR, and Consumer Remote Control Timing |     |

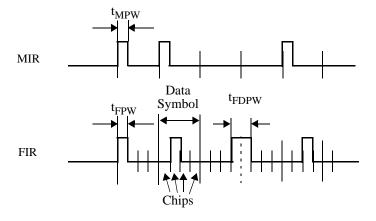

| Figure 7-38 | Fast IR Timing (MIR and FIR)                            |     |

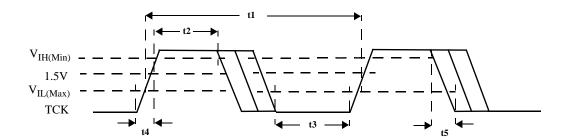

| Figure 7-39 | TCK Timing and Measurement Points                       |     |

| Figure 7-40 | GPIO Output Timing Measurement Conditions               |     |

| Figure 7-41 | GPIO Input Timing Measurement Conditions                |     |

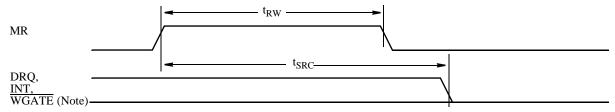

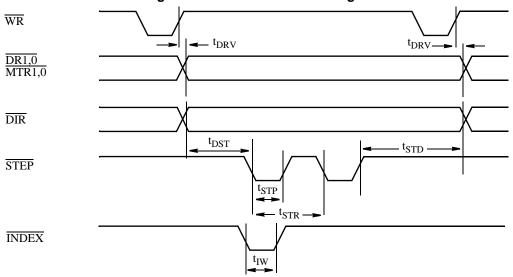

| Figure 7-42 | Floppy Disk Reset Timing                                | 531 |

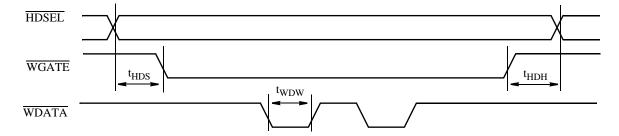

| Figure 7-43 | Write Data Timing                                       | 532 |

| Figure 7-44 | Drive Control Timing                                    |     |

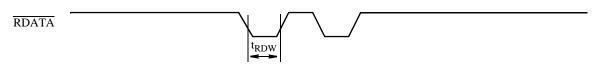

| Figure 7-45 | Read Data Timing                                        |     |

| Figure 7-46 | KBC Signals Rising and Falling                          |     |

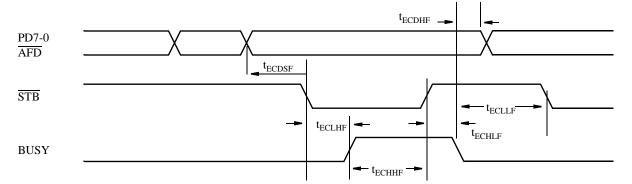

| Figure 7-47 | Parallel Port Interrupt Timing (Compatible Mode)        |     |

| Figure 7-48 | Parallel Port Interrupt Timing (Extended Mode)          |     |

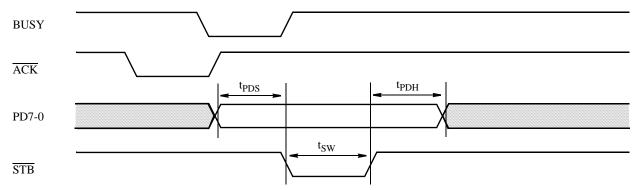

| Figure 7-49 | Typical Parallel Port Data Exchange                     |     |

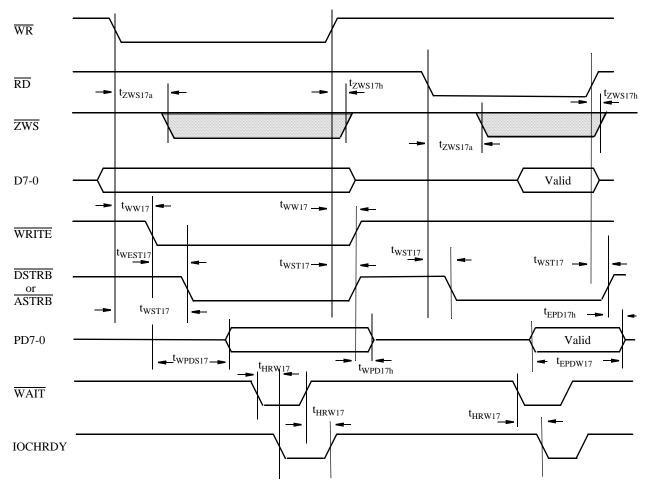

| Figure 7-50 | Enhanced Parallel Port 1.7 Timing                       |     |

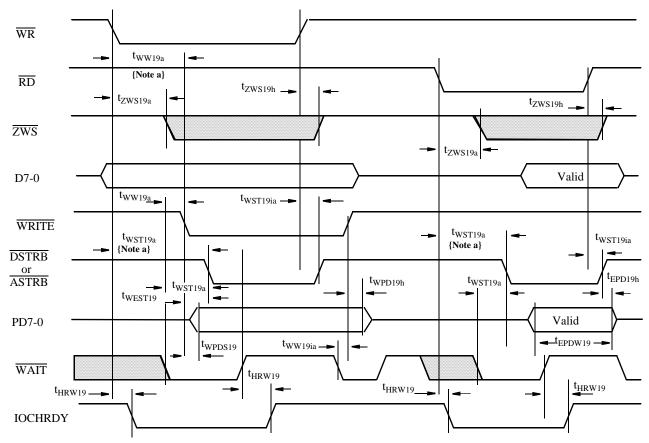

| Figure 7-51 | Enhanced Parallel Port 1.9 Timing                       |     |

| Figure 7-52 | ECP Parallel Port Forward Timing Diagram                |     |

| Figure 7-53 | ECP Parallel Port Backward Timing Diagram               |     |

|             |                                                         |     |

# List of Figures

| Figure 7-54    | ZF-Logic Output Timing Measurement Conditions | 540 |

|----------------|-----------------------------------------------|-----|

|                | ZF-Logic Input Timing Measurement Conditions  |     |

| 8. Pinout Sum  | ımary                                         | 541 |

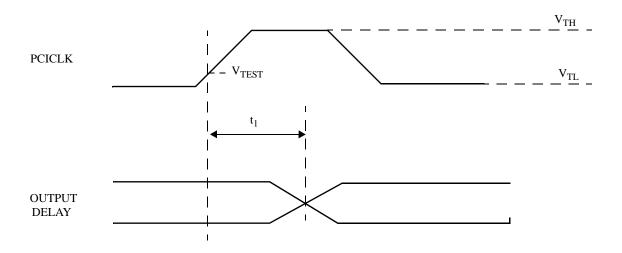

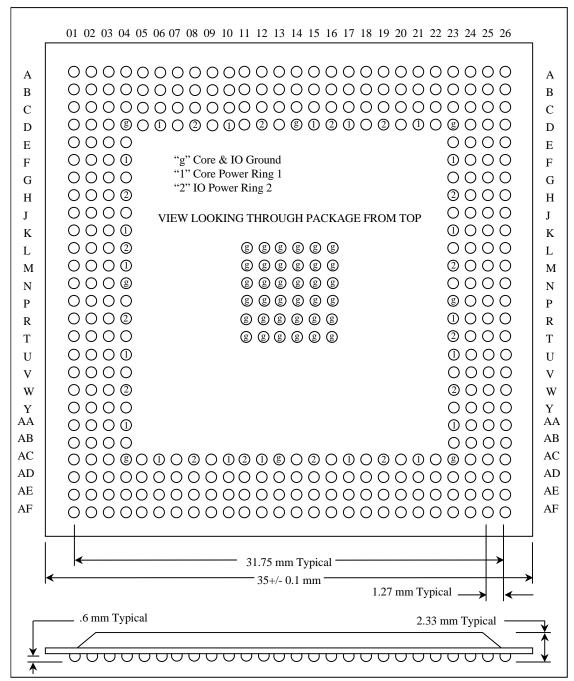

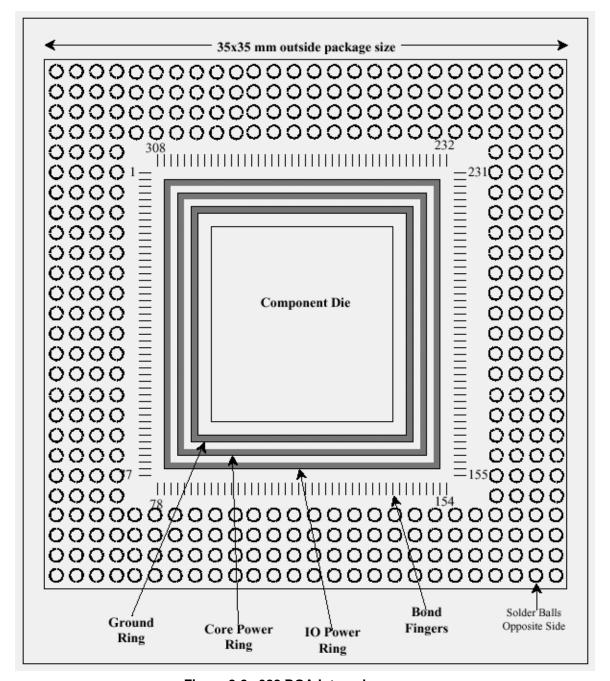

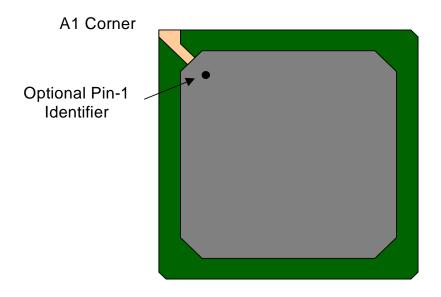

| Figure 8-1     | ZFx86 Package - Solder Balls                  | 542 |

|                | 388 BGA Internal                              |     |

| Figure 8-1     | ZFx86 Orientation                             | 544 |

| 9. BUR API     |                                               | 587 |

| 10. Signal Sta | tus After POST                                | 597 |

| 11. Phoenix B  | IOS Register Settings                         | 603 |

| Index          |                                               | 653 |

| Table of Con             | tents                                                        | 7  |

|--------------------------|--------------------------------------------------------------|----|

| List of Figure           | es                                                           | 13 |

| List of Tables           | S                                                            | 17 |

| 1. Overview              |                                                              | 29 |

|                          | Processor                                                    |    |

|                          |                                                              |    |

| Table 2.1<br>Table 2.2   | Initialized Register Controls                                |    |

| Table 2.3                | Segment Register Selection Rules                             |    |

| Table 2.4                | EFLAGS Register                                              |    |

| Table 2.5                | System Register Set                                          |    |

| Table 2.6                | Control Registers Map                                        |    |

| Table 2.7                | CR3, CR2, and CR0 Bit Definitions                            |    |

| Table 2.8                | Effects of Various Combinations of TS, EM and MP Bits        |    |

| Table 2.9                | Application and System Segment Descriptors                   |    |

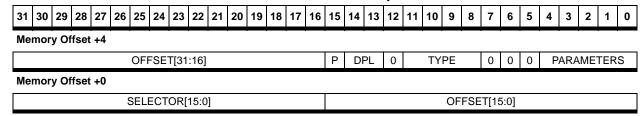

| Table 2.10               | Gate Descriptors                                             |    |

| Table 2.11               | Gate Descriptor Bit Definitions                              |    |

| Table 2.12               | 32-Bit Task State Segment (TSS) Table                        |    |

| Table 2.13               | 16-Bit Task State Segment (TSS) Table                        |    |

| Table 2.14               | Configuration Register Map                                   |    |

| Table 2.15               | CCR1 Bit Definitions                                         | 49 |

| Table 2.16               | CCR2 Bit Definitions                                         | 51 |

| <b>Table 2.17</b>        | CCR3 Bit Definitions                                         | 51 |

| Table 2.18               | SMAR Size Field                                              | 52 |

| Table 2.19               | DIR0 Bit Definitions                                         |    |

| Table 2.20               | DIR1 Bit Definitions                                         |    |

| Table 2.21               | Debug Registers                                              |    |

| Table 2.22               | DR6 and DR7 Field Definitions                                |    |

| Table 2.23               | Test Registers                                               |    |

| Table 2.24               | TR7 and TR6 Bit Definitions                                  |    |

| Table 2.25               | TR6 Attribute Bit Pairs                                      |    |

| Table 2.26               | TR3-TR5 Bit Definitions                                      |    |

| Table 2.27               | Memory Addressing Modes                                      |    |

| Table 2.28               | Directory and Page Table Entry (DTE and PTE) Bit Definitions |    |

| Table 2.29               | Interrupt Vector Assignments                                 |    |

| Table 2.30               | Interrupt and Exception Priorities                           |    |

| Table 2.31               | Exception Changes in Real Mode                               |    |

| Table 2.32               | Error Code Bit Definitions                                   |    |

| Table 2.33<br>Table 2.34 | Requirement for Recognizing SMI# and SMINT                   |    |

| Table 2.35               | SMM Memory Space HeaderSMM Instruction Set                   |    |

| Table 2.36               | SMM Pin Definitions                                          |    |

| Table 2.37               | Descriptor Types Used for Control Transfer                   |    |

| Table 2.38               | Status Control Register Bit Definitions                      |    |

| Table 2.39               | Mode Control Register Bit Definition                         |    |

| 1 4510 2.00              |                                                              |    |

| <b>Table 2.40</b>                      | Instruction Fields                                                                                                                                                                                | 87                |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <b>Table 2.41</b>                      | Instruction Prefix Summary                                                                                                                                                                        | 87                |

| <b>Table 2.42</b>                      | w Field Encoding                                                                                                                                                                                  | 88                |

| Table 2.43                             | d Field Encoding                                                                                                                                                                                  | 88                |

| Table 2.44                             | eee Field Encoding                                                                                                                                                                                | 88                |

| Table 2.45                             | mod r/m Field Encoding                                                                                                                                                                            |                   |

| Table 2.46                             | mod r/m Field Encoding Dependent on w Field                                                                                                                                                       | 90                |

| Table 2.47                             | reg Field                                                                                                                                                                                         |                   |

| Table 2.48                             | sreg3 Field Encoding                                                                                                                                                                              | 90                |

| Table 2.49                             | sreg2 Field Encoding                                                                                                                                                                              | 91                |

| Table 2.50                             | ss Field Encoding                                                                                                                                                                                 | 91                |

| Table 2.51                             | index Field Encoding                                                                                                                                                                              | 91                |

| Table 2.52                             | mod base Field Encoding                                                                                                                                                                           |                   |

| Table 2.53                             | CPU Clock Count Abbreviations                                                                                                                                                                     |                   |

| Table 2.54                             | Flag Abbreviations                                                                                                                                                                                |                   |

| Table 2.55                             | Action of Instruction on Flag                                                                                                                                                                     |                   |

| Table 2.56                             | Processor Core Instruction Set Summary                                                                                                                                                            |                   |

| Table 2.57                             | FPU Table Abbreviations                                                                                                                                                                           |                   |

| Table 2.58                             | MMX Instruction Set Summary                                                                                                                                                                       | 108               |

| 3. North Bridg                         | e                                                                                                                                                                                                 | 113               |

| Table 3.1                              | SDRAM Interface Signals                                                                                                                                                                           | 116               |

| Table 3.2                              | PCI Sideband Signals                                                                                                                                                                              |                   |

| Table 3.3                              | Test Signals (JTAG)                                                                                                                                                                               |                   |

| Table 3.4                              | Memory Access Map                                                                                                                                                                                 |                   |

| Table 3.5                              | I/O Address Map                                                                                                                                                                                   |                   |

| Table 3.6                              | North Bridge Core Burst Sequence                                                                                                                                                                  |                   |

| Table 3.7                              | SDRAM Configurations                                                                                                                                                                              |                   |

| Table 3.8                              | ROM Shadow Illustration                                                                                                                                                                           |                   |

| Table 3.9                              | North Bridge Registers                                                                                                                                                                            | 126               |

| Table 3.10                             | CPU-PCI Cycle Conversion                                                                                                                                                                          |                   |

| Table 3.11                             | Configuration Registers                                                                                                                                                                           |                   |

| Table 3.12                             | SMM Control Register (SMMC)                                                                                                                                                                       |                   |

| Table 3.13                             | Processor Control Register (PROC)                                                                                                                                                                 |                   |

| Table 3.14                             | Write FIFO Control Register (WFIFOC)                                                                                                                                                              |                   |

| Table 3.15                             | PCI Control Register (PCIC)                                                                                                                                                                       | 145               |

| Table 3.16                             | Clock Skew Adjust Register (CSA)                                                                                                                                                                  |                   |

| Table 3.17                             | BUS MASTER And Snooping Control Register (SNOOPCTRL)                                                                                                                                              | 146               |

| Table 3.18                             | Arbiter Control Register (ARBCTRL)                                                                                                                                                                | 148               |

| Table 3.19                             | PCI Write FIFO Control Register (PCIWFIFOC)                                                                                                                                                       | 148               |

|                                        | PCI Write FIFO Control Register (PCIWFIFOC)                                                                                                                                                       |                   |

| Table 3.20                             | Shadow RAM Read Enable Control Register (SHADRC)                                                                                                                                                  |                   |

| Table 3.20<br>Table 3.21               |                                                                                                                                                                                                   | 149               |

|                                        | Shadow RAM Read Enable Control Register (SHADRC)                                                                                                                                                  | 149<br>150<br>151 |

| Table 3.21                             | Shadow RAM Read Enable Control Register (SHADRC)                                                                                                                                                  | 149<br>150<br>151 |

| Table 3.21<br>Table 3.22               | Shadow RAM Read Enable Control Register (SHADRC) Shadow RAM Write Enable Control Register Bank 0 Control Register (N_B0C) Bank 0 Timing Control Register (N_B0TC) Bank 1 Control Register (N_B1C) |                   |

| Table 3.21<br>Table 3.22<br>Table 3.23 | Shadow RAM Read Enable Control Register (SHADRC)                                                                                                                                                  |                   |

|    | Table 3.27   | Bank 2 Timing Control Register (N_B2TC)                       | 154 |

|----|--------------|---------------------------------------------------------------|-----|

|    | Table 3.28   | Bank 3 Control Register (N_B3C)                               |     |

|    | Table 3.29   | Bank 3 Timing Control Register (N_B3TC)                       |     |

|    | Table 3.30   | DRAM Configuration Register 1 (DCONF1)                        |     |

|    | Table 3.31   | DRAM Configuration Register 2 (DCONF2)                        |     |

|    | Table 3.32   | DRAM Refresh Control Register (DRFSHC)                        | 158 |

|    | Table 3.33   | SDRAM Mode Program Register (SDRAMMPR)                        | 158 |

|    | Table 3.34   | SDRAM Mode Program Register (SDRAMMPREX)                      |     |

|    | Table 3.35   | SDRAM Slew Control Register (SDRAMSLEW)                       | 159 |

|    | Table 3.36   | Clock Control Register (CC)                                   |     |

|    | Table 3.37   | Clock Control2 Register (CC2)                                 | 161 |

|    | Table 3.38   | CPU-SYNC Register (CPUSYNC)                                   |     |

|    | Table 3.39   | Vendor ID Register (VID)                                      |     |

|    | Table 3.40   | Device ID Register (DID)                                      |     |

|    | Table 3.41   | Command Register (COMMD)                                      | 162 |

|    | Table 3.42   | Status Register (STAT)                                        |     |

|    | Table 3.43   | Revision ID Register (RID)                                    |     |

|    | Table 3.44   | Class Register (CLASS)                                        | 163 |

| 4. | South Bridge | e                                                             | 165 |

|    | Table 4.1    | Logical Devices                                               |     |

|    | Table 4.2    | System Interface Signals                                      |     |

|    | Table 4.3    | Clock and Crystal Interface Signals                           |     |

|    | Table 4.4    | CPU Interface Signals                                         |     |

|    | Table 4.5    | Back-Side PCI Bus Interface Signals                           |     |

|    | Table 4.6    | IDE Interface Signals                                         |     |

|    | Table 4.7    | USB Interface Signals                                         |     |

|    | Table 4.8    | GPIO Interface Signals                                        |     |

|    | Table 4.9    | Full ISA Interface                                            |     |

|    | Table 4.10   | Access Bus                                                    | 189 |

|    | Table 4.11   | Clock                                                         |     |

|    | Table 4.12   | Floppy Disk Controller                                        | 189 |

|    | Table 4.13   | Keyboard and Mouse Controller (KBC)                           | 190 |

|    | Table 4.14   | Parallel Port                                                 | 192 |

|    | Table 4.15   | Power and Ground                                              | 193 |

|    | Table 4.16   | Serial Port 1 and Serial Port 2 (Shared with I/R Port)        | 194 |

|    | Table 4.17   | Infrared Communication Port (Shared W/COM2)                   | 195 |

|    | Table 4.18   | PCI Configuration Address Register (0CF8h)                    |     |

|    | Table 4.19   | F0: PCI Header/Bridge and GPIO Configuration Register Summary | 197 |

|    | Table 4.20   | F0BAR0: GPIO Support Registers Summary                        |     |

|    | Table 4.21   | F1: PCI Header Registers for SMI Status Summary               | 200 |

|    | Table 4.22   | F1BAR0: SMI Status Registers Summary                          |     |

|    | Table 4.23   | F2: PCI Header Registers for IDE Controller Support Summary   |     |

|    | Table 4.24   | IDE Controller Configuration Summary                          |     |

|    | Table 4.25   | F3: PCI Header Registers for XBus Expansion Summary           |     |

|    | Table 4.26   | F3BAR0: XBus Expansion Registers Summary                      |     |

|    | Table 4.27   | PCIUSB: USB Controller Register Summary                       | 203 |

| Table 4.28  | ZF-Logic Register Summary                                         | 204 |

|-------------|-------------------------------------------------------------------|-----|

| Table 4.29  | Legacy I/O Register Summary                                       |     |

| Table 4.30  | F0 Index xxh: PCI Header and Bridge Configuration Registers       |     |

| Table 4.31  | F0BAR0+I/O Offset xxh: GPIO Runtime and Configuration Registers . |     |

| Table 4.32  | F1 Index xxh: PCI Header Registers for SMI Status                 |     |

| Table 4.33  | F1BAR0+I/O Offset xxh: SMI Status Registers                       |     |

| Table 4.34  | F2 Index xxh: PCI Header/Channels 0 & 1 Registers for             |     |

|             | IDE Controller Config                                             | 236 |

| Table 4.35  | F2BAR4+I/O Offset xxh: IDE Controller Configuration Registers     |     |

| Table 4.36  | F3 Index xxh: PCI Header Registers for XBus Expansion             |     |

| Table 4.37  | F3BAR0+I/O Offset xxh: XBus Expansion Registers                   |     |

| Table 4.38  | PCIUSB: USB Controller Registers                                  |     |

| Table 4.39  | DMA Channel Control Registers                                     |     |

| Table 4.40  | DMA Page Registers                                                |     |

| Table 4.41  | Programmable Interval Timer Registers                             |     |

| Table 4.42  | Programmable Interrupt Controller Registers                       |     |

| Table 4.43  | Keyboard Controller Registers                                     |     |

| Table 4.44  | Real-Time Clock Registers                                         |     |

| Table 4.45  | Miscellaneous Registers                                           |     |

| Table 4.46  | ACCESS.bus Interface (ACB)                                        |     |

| Table 4.47  | SuperI/O Configuration Options                                    |     |

| Table 4.48  | Logical Device Number (LDN) Assignments                           |     |

| Table 4.49  | Standard Control Registers                                        |     |

| Table 4.50  | Logical Device Activate Register                                  |     |

| Table 4.51  | I/O Space Configuration Registers                                 |     |

| Table 4.52  | Interrupt Configuration Registers                                 |     |

| Table 4.53  | DMA Configuration Registers                                       |     |

| Table 4.54  | Special Logical Device Configuration Registers                    |     |

| Table 4.55  | Register Type Abbreviations                                       |     |

| Table 4.56  | SuperI/O Configuration Registers                                  |     |

| Table 4.57  | SuperI/O ID Register (SID) - Index 20H                            |     |

| Table 4.58  | SuperI/O Configuration 1 Register (SIOCF1) - Index 21H            |     |

| Table 4.59  | SuperI/O Configuration 2 Register (SIOCF2) - Index 22H            |     |

| Table 4.60  | SuperI/O Revision ID Register (SRID) - Index 27H                  |     |

| Table 4.61  | FDC Registers                                                     |     |

| Table 4.62  | Logical Device 0 (FDC) Configuration                              | 273 |

| Table 4.63  | FDC Configuration Register - Index F0H                            |     |

| Table 4.64  | Drive ID Register - Index F1H                                     |     |

| Table 4.65  | Parallel Port Configuration Registers                             |     |

| Table 4.66  | Parallel Port Configuration Register - F0H                        | 275 |

| Table 4.67  | Banks 0 and 1 - The Common Control and Status Register Map        |     |

| Table 4.68  | Bank 0 - PS/2 KBD/MOUSE Wake-Up Config/Control Register Map       |     |

| Table 4.69  | Bank 1 - CEIR Wake-Up Config/Control Register Map                 |     |

| Table 4.70  | Wake-Up Events Status Register (WKSR) - 00H                       |     |

| Table 4.70  | Wake-Up Events Control Register (WKCR) - 01H                      |     |

| Table 4.71  | Wake-Up Configuration Register (WKCFG) - 02H                      |     |

| Table 4.72  | PS/2 Protocol Control Register (PS2CTL) (Bank 0 Offset 03H)       |     |

| Table 4.73  | Keyboard Data Shift Register (KDSR) - Bank 0 Offset 06H           |     |

| 1 ablt 4.14 | Reyboard Data Shirt Register (RDSR) - Darik U Chisel Will         | 204 |

| Table 4.75  | Mouse Data Shift Register (MDSR) 07H                         | 284 |

|-------------|--------------------------------------------------------------|-----|

| Table 4.76  | PS/2 Keyboard Key Data Registers (PS2KEY0 - PS2KEY7)         |     |

| Table 4.77  | CEIR Wake-Up Control Register (IRWCR) - Bank 1 Offset 3      |     |

| Table 4.78  | CEIR Wake-Up Address Register (IRWAD) - Bank 1 Offset 05H    |     |

| Table 4.79  | CEIR Wake-Up Address Mask Register (IRWAM) - Bank 1 Offset 6 |     |

| Table 4.80  | CEIR Address Shift Register (ADSR) - Bank 1 Offset 7         |     |

| Table 4.81  | CEIR Wake-Up Range 0 Registers - IRWTR0L- Bank 1 Offset 8    |     |

| Table 4.82  | CEIR Wake-Up Range 0 Registers - IRWTR0H - Bank 1 Offset 9   |     |

| Table 4.83  | CEIR Wake-Up Range 1 Registers - IRWTR1L - Bank 1 Offset 0AH |     |

| Table 4.84  | CEIR Wake-Up Range 1 Registers - IRWTR1H - Bank 1 Offset 0BH |     |

| Table 4.85  | CEIR Wake-Up Range 2 Registers - IRWTR2L - Bank 1 0CH)       |     |

| Table 4.86  | CEIR Wake-Up Range 2 Registers - IRWTR2H - Bank 1 0DH        | 289 |

| Table 4.87  | CEIR Wake-Up Range 3 Registers - IRWTR3L - Bank 1 OEH        | 289 |

| Table 4.88  | CEIR Wake-Up Range 3 Registers - IRWTR3H - Bank 1 OFH        | 290 |

| Table 4.89  | Time Range Limits for CEIR Protocols                         | 290 |

| Table 4.90  | Banks 0 and 1 - The Common Three-Register Map                | 291 |

| Table 4.91  | Bank 0 - PS/2 Keyboard/Mouse Wake-Up Config/Ctrl Registers   |     |

| Table 4.92  | CEIR Wake-Up Configuration and Control Registers             | 291 |

| Table 4.93  | Serial Ports 1 and 2 Configuration Registers                 | 292 |

| Table 4.94  | Serial Ports 1 and 2 Configuration Register - F0H            | 293 |

| Table 4.95  | System Wake-Up Control (SWC) Configuration                   | 294 |

| Table 4.96  | Mouse Configuration Registers                                | 295 |

| Table 4.97  | Keyboard Configuration Registers                             | 296 |

| Table 4.98  | iKBC Configuration Register - F0H                            | 296 |

| Table 4.99  | Infrared Communication Port Configuration Registers          | 297 |

| Table 4.100 | Infrared Communication Port Configuration Register - F0H     |     |

| Table 4.101 | ACB Runtime Registers                                        |     |

| Table 4.102 | Access Bus Interface (ACB) Configuration                     |     |

| Table 4.103 | ACB Configuration Register – F0H                             |     |

| Table 4.104 | Logical Device A (RTC) Configuration                         |     |

| Table 4.105 | RAM Lock Register (RLR) - F0H                                |     |

| Table 4.106 | Date Of Month Alarm Register Offset (DOMAO) – F1H            |     |

| Table 4.107 | Month Alarm Register Offset (MAO) – F2H                      |     |

| Table 4.108 | Century Register Offset (CENO0) – F3H                        |     |

| Table 4.109 | RTC Configuration Register Map                               |     |

| Table 4.110 | RAM Lock Register (RLR)                                      | 307 |

| Table 4.111 | Date Of Month Alarm Register Offset (DOMAO)                  |     |

| Table 4.112 | Month Alarm Register Offset (DOMAO)                          |     |

| Table 4.113 | Century Register Offset (CENO)                               |     |

| Table 4.114 | RTC Configuration Register Bitmap                            |     |

| Table 4.115 | RTC Register Map                                             |     |

| Table 4.116 | Seconds Register (SEC)) – Index 00H                          |     |

| Table 4.117 | Seconds Alarm Register (SECA)) – 01H                         |     |

| Table 4.118 | Minutes Register (MIN)) – 02H                                |     |

| Table 4.119 | Minutes Alarm Register (MINA) – 03H                          |     |

| Table 4.120 | Hours Register (HOR) – 04H                                   | 312 |

| Table 4.121 | Hours Alarm Register (HORA) – 05H                            | 312 |

| Table 4.122 | Day Of Week Register (DOW) – 06H                     | 312 |

|-------------|------------------------------------------------------|-----|

| Table 4.123 | Date Of Month Register (DOM) – 07H                   | 313 |

| Table 4.124 | Month Register (MON) - 08H                           | 313 |

| Table 4.125 | Year Register (YER) - 09H                            | 313 |

| Table 4.126 | RTC Control Register A (CRA) – 0AH                   | 314 |

| Table 4.127 | Divider Chain Control and Test Selection             | 314 |

| Table 4.128 | Periodic Interrupt Rate Encoding                     | 315 |

| Table 4.129 | RTC Control Register B (CRB) - 0BH                   | 316 |

| Table 4.130 | RTC Control Register C (CRC) - 0CH                   | 318 |

| Table 4.131 | RTC Control Register D (CRD) - 0DH                   | 319 |

| Table 4.132 | Date of Month Alarm Register (DOMA)                  | 319 |

| Table 4.133 | Month Alarm Register (MONA)                          | 319 |

| Table 4.134 | Century Register (CEN)                               | 320 |

| Table 4.135 | BCD and Binary Formats                               | 320 |

| Table 4.136 | RTC Register Bitmap                                  | 321 |

| Table 4.137 | Standard RAM Map                                     | 321 |

| Table 4.138 | Extended RAM Map                                     | 321 |

| Table 4.139 | ACB Register Map                                     | 329 |

| Table 4.140 | ACB Serial Data Register (ACBSDA) - 00H              | 329 |

| Table 4.141 | ACB Status Register (ACBST) - 01H                    |     |

| Table 4.142 | ACB Control Status Register (ACBCST) - 02H           |     |

| Table 4.143 | ACB Control Register 1 (ACBCTL1) - 03H               |     |

| Table 4.144 | ACB Own Address Register (ACBADDR) - 04H             |     |

| Table 4.145 | ACB Control Register 2 (ACBCTL2) - 05H               |     |

| Table 4.146 | ACB Register Bitmap                                  |     |

| Table 4.147 | KBC Register Map                                     |     |

| Table 4.148 | KBC Bitmap Summary                                   |     |

| Table 4.149 | FDC Register Map                                     |     |

| Table 4.150 | FDC Bitmap Summary                                   |     |

| Table 4.151 | Parallel Port Register Map for First Level Offset    |     |

| Table 4.152 | Parallel Port Register Map for Second Level Offset   |     |

| Table 4.153 | Parallel Port Bitmap Summary for First Level Offset  |     |

| Table 4.154 | Parallel Port Bitmap Summary for Second Level Offset |     |

| Table 4.155 | Bank 0 Register Map                                  |     |

| Table 4.156 | Bank Selection Encoding                              |     |

| Table 4.157 | Bank 1 Register Map                                  |     |

| Table 4.158 | Bank 2 Register Map                                  |     |

| Table 4.159 | Bank 3 Register Map                                  |     |

| Table 4.160 | Bank 0 Bitmap                                        |     |

| Table 4.161 | Bank 1 Bitmap                                        |     |

| Table 4.162 | Bank 2 Bitmap                                        |     |

| Table 4.163 | Bank 3 Bitmap                                        |     |

| Table 4.164 | Register Bank Summary                                |     |

| Table 4.165 | Bank 0 Register Map                                  |     |

| Table 4.166 | Interrupt Enable Register (IER, Non-Extended Mode)   |     |

| Table 4.167 | Non-Extended Mode Interrupt Priorities               |     |

| Table 4.168 | Bit Settings for Parity Control                      | 364 |

| Table 4.169 Bank Selection Encoding                                                                                                        | 372<br>373               |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Table 4.171 Bank 1 Register Map Table 4.172 Bits Cleared on Fallback Table 4.173 Baud Generator Divisor Settings Table 4.174 Bank 1 Bitmap | 373                      |

| Table 4.172 Bits Cleared on Fallback Table 4.173 Baud Generator Divisor Settings Table 4.174 Bank 1 Bitmap                                 |                          |

| Table 4.173 Baud Generator Divisor Settings Table 4.174 Bank 1 Bitmap                                                                      | 27/                      |

| Table 4.174 Bank 1 Bitmap                                                                                                                  | 3/4                      |

| Table 4.174 Bank 1 Bitmap                                                                                                                  | 374                      |

|                                                                                                                                            |                          |

| Table 4.175 Bank 2 Register Map                                                                                                            |                          |

| Table 4.176 DMA Threshold Levels                                                                                                           |                          |

| Table 4.177 Bank 2 Bitmap                                                                                                                  |                          |

| Table 4.178 Bank 3 Register Map                                                                                                            |                          |

| Table 4.179 Bank 3 Bitmap                                                                                                                  |                          |

| Table 4.180 Bank 4 Register Map                                                                                                            |                          |

| Table 4.181 Bank 4 Bitmap                                                                                                                  |                          |

| Table 4.182 Bank 5 Register Map                                                                                                            |                          |

| Table 4.183 Bank 5 Bitmap                                                                                                                  |                          |

| Table 4.184 Bank 6 Register Map                                                                                                            |                          |

| Table 4.185 IMIR Pulse Width Settings                                                                                                      |                          |

| Table 4.186 MIR Beginning Flags                                                                                                            |                          |

| Table 4.187 FIR Preamble Length                                                                                                            |                          |

| Table 4.188 Bank 6 Bitmap                                                                                                                  |                          |

| Table 4.189 Bank 7 Register Map                                                                                                            |                          |

| Table 4.190 CEIR, Low Speed Demodulator (RXHSC = 0)                                                                                        |                          |

| Table 4.191 Consumer IR High Speed Demodulator (RXHSC = 1)                                                                                 |                          |

| Table 4.192 Sharp-IR Demodulator                                                                                                           |                          |

| Table 4.193 Carrier Clock Pulse Width Options (Frequency Ranges in KHz)                                                                    |                          |

| Table 4.194 CEIR Carrier Frequency Encoding (Frequency Ranges in KHz)                                                                      |                          |

| Table 4.195 Infrared Receiver Input Selection                                                                                              |                          |

| Table 4.196 Bank 7 Bitmap                                                                                                                  |                          |

| ·                                                                                                                                          |                          |

| 5. ZF-Logic and Clocking                                                                                                                   |                          |

| Table 5.1 Access to ZFL                                                                                                                    |                          |

| Table 5.2 ZF-Logic Complete Index                                                                                                          |                          |

| Table 5.3 ZF-Logic Pin List                                                                                                                | 409                      |

| Table 5.4 Memory Mapper Pins                                                                                                               |                          |

| Table 5.5 Indices For Memory Windows                                                                                                       |                          |

| Table 5.6 Memory Window "N" Base Low - Bits 15:12 (nibble 3)                                                                               |                          |

| Table 5.7 Memory Window "N" Base High - Bits 23:16 (nibbles 5-4)                                                                           | 412                      |

| Table 5.8 Memory Window "N" Size Low - (nibble 3)                                                                                          | 412                      |

| Table 5.9 Memory Window "N" Size High - (nibbles 5-4)                                                                                      |                          |

| Table F 10 Mamory Window "N! Dags Low (nibble 2)                                                                                           | 412                      |

| Table 5.10 Memory Window "N' Page Low - (nibble 3)                                                                                         |                          |

| Table 5.10 Memory Window "N' Page Low - (nibble 3)                                                                                         | 4.4                      |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     |                          |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     |                          |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     | 413                      |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     | 413<br>414               |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     | 413<br>414<br>422        |

| Table 5.11 Memory Window "N" Page High - (nibbles 5-4)                                                                                     | 413<br>414<br>422<br>423 |

| Table 5.19     | I/O Window "N" Base High Format                 | 424 |

|----------------|-------------------------------------------------|-----|

| Table 5.20     | ZF-Logic Index for the Watchdog Timers          | 426 |

| Table 5.21     | Watchdog 1 Count Low Byte Index 0CH             | 426 |

| Table 5.22     | Watchdog 1 Count High Byte Index 0DH            | 426 |

| Table 5.23     | Watchdog Generated Reset Pulse Length Index 0FH | 427 |

| Table 5.24     | Watchdog Control Low Index 10H                  |     |

| Table 5.25     | Watchdog Control High Index 11H                 |     |

| Table 5.26     | Watchdog Status Index 12H                       | 429 |

| Table 5.27     | ZF-Logic Index for the PWM Generator            |     |

| Table 5.28     | PWM Prescaler Low Byte - Index 04H              | 431 |

| Table 5.29     | PWM Prescaler High Byte - Index 05h             | 431 |

| Table 5.30     | PWM duty cycle - Index 06h                      |     |

| Table 5.31     | PWM I/O Control Index 08H                       | 432 |

| Table 5.32     | PWM Read Output Index 0AH                       | 432 |